Uart, Data transmission, Figure 41 – Rainbow Electronics AT90LS8535 User Manual

Page 59

59

AT90S/LS8535

1041H–11/01

UART

The AT90S8535 features a full duplex (separate receive and transmit registers) Univer-

sal Asynchronous Receiver and Transmitter (UART). The main features are:

•

Baud Rate Generator that can Generate a Large Number of Baud Rates (bps)

•

High Baud Rates at Low XTAL Frequencies

•

8 or 9 Bits Data

•

Noise Filtering

•

Overrun Detection

•

Framing Error Detection

•

False Start Bit Detection

•

Three Separate Interrupts on TX Complete, TX Data Register Empty and RX Complete

•

Buffered Transmit and Receive

Data Transmission

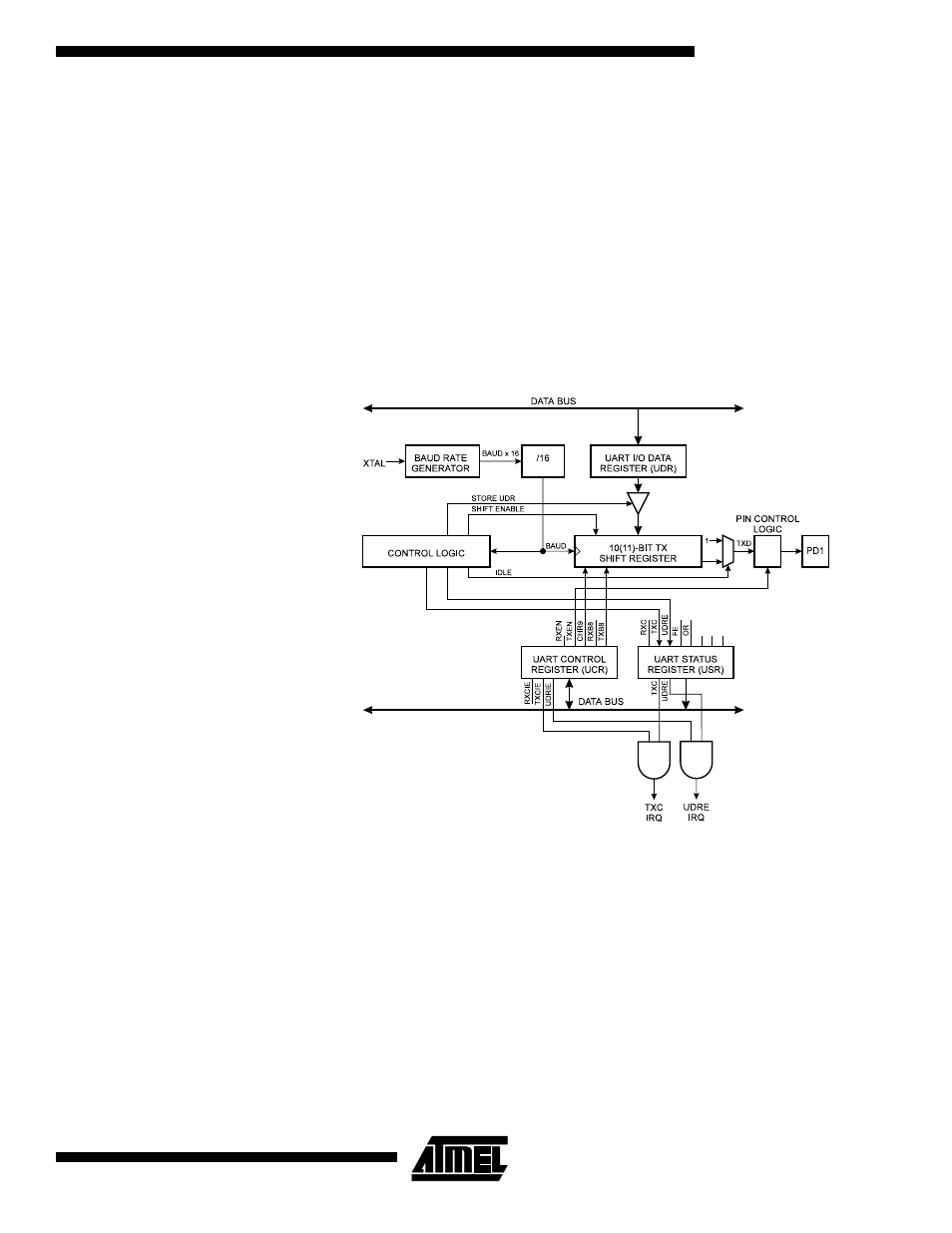

A block schematic of the UART transmitter is shown in Figure 41.

Figure 41. UART Transmitter

Data transmission is initiated by writing the data to be transmitted to the UART I/O Data

Register, UDR. Data is transferred from UDR to the Transmit shift register when:

•

A new character is written to UDR after the stop bit from the previous character has

been shifted out. The shift register is loaded immediately.

•

A new character is written to UDR before the stop bit from the previous character

has been shifted out. The shift register is loaded when the stop bit of the character

currently being transmitted is shifted out.

If the 10(11)-bit Transmitter shift register is empty, data is transferred from UDR to the

shift register. The UDRE (UART Data Register Empty) bit in the UART Status Register,

USR, is set. When this bit is set (one), the UART is ready to receive the next character.

At the same time as the data is transferred from UDR to the 10(11)-bit shift register, bit 0

of the shift register is cleared (start bit) and bit 9 or 10 is set (stop bit). If 9-bit data word