Block diagram, Memory array – Rainbow Electronics AT45DB081D User Manual

Page 4

4

3596N–DFLASH–11/2012

AT45DB081D

3.

Block Diagram

4.

Memory Array

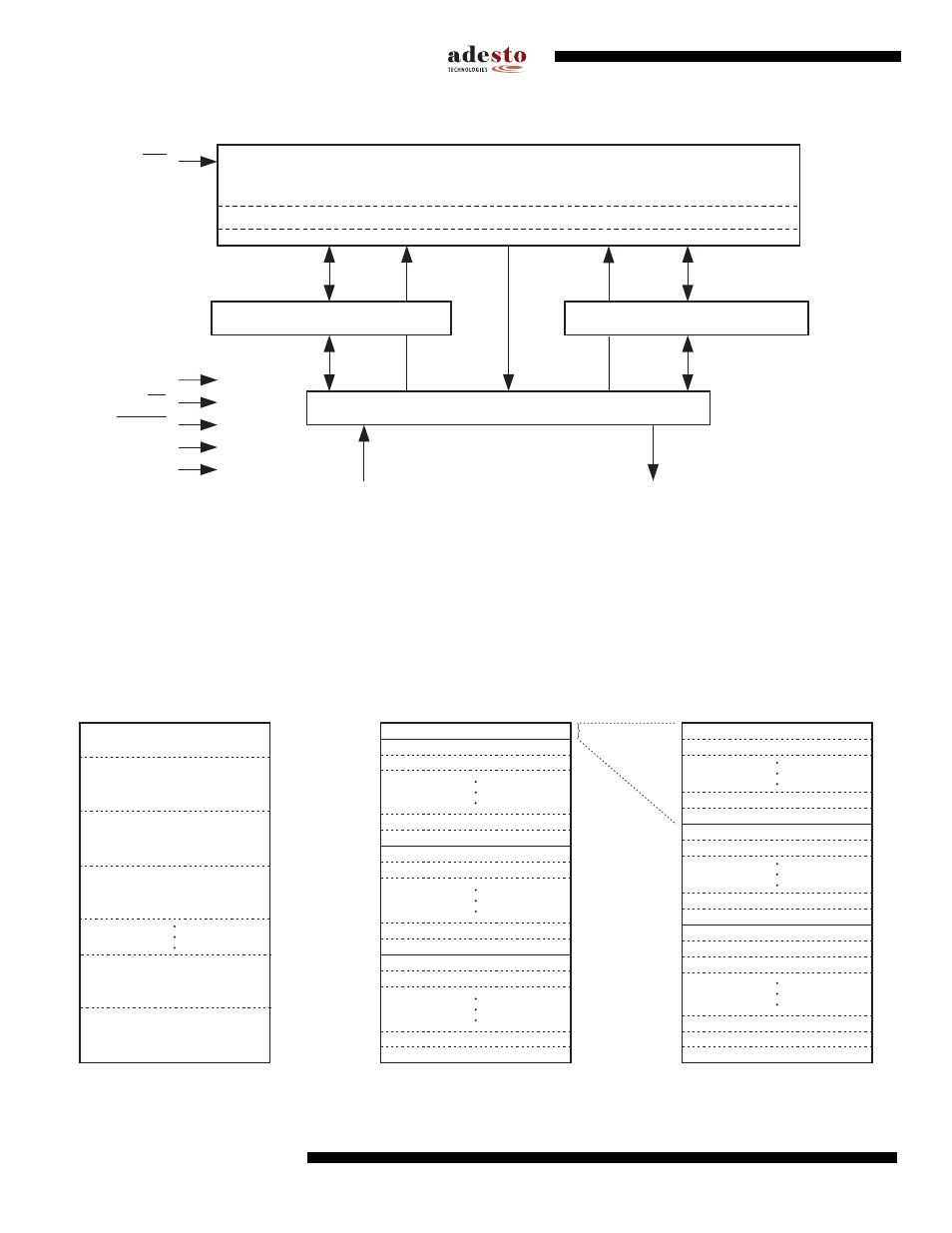

To provide optimal flexibility, the memory array of the AT45DB081D is divided into three levels of granularity comprising of

sectors, blocks, and pages. The “Memory Architecture Diagram” illustrates the breakdown of each level and details the

number of pages per sector and block. All program operations to the DataFlash occur on a page by page basis. The erase

operations can be performed at the chip, sector, block or page level.

Figure 4-1.

Memory Architecture Diagram

FLASH MEMORY ARRAY

PAGE (256-/264-BYTES)

BUFFER 2 (256-/264-BYTES)

BUFFER 1 (256-/264-BYTES)

I/O INTERFACE

SCK

CS

RESET

VCC

GND

WP

SO

SI

SECTOR 0a = 8 Pages

2,048-/2,112-bytes

SECTOR 0b = 248 Pages

63,488-/65,472-bytes

Block = 2,048-/2,112-bytes

8 Pages

SECTOR 0a

SECT

OR 0b

Page = 256-/264-bytes

PAGE 0

PAGE 1

PAGE 6

PAGE 7

PAGE 8

PAGE 9

PAGE 4,094

PAGE 4,095

BLOCK 0

PAGE 14

PAGE 15

PAGE 16

PAGE 17

PAGE 18

BLOCK 1

SECTOR ARCHITECTURE

BLOCK ARCHITECTURE

PAGE ARCHITECTURE

BLOCK 0

BLOCK 1

BLOCK 30

BLOCK 31

BLOCK 32

BLOCK 33

BLOCK 510

BLOCK 511

BLOCK 62

BLOCK 63

BLOCK 64

BLOCK 65

SECT

OR 1

SECTOR 15 = 256 Pages

65,536-/67,584-bytes

BLOCK 2

SECTOR 1 = 256 Pages

65,536-/67,584-bytes

SECTOR 14 = 256 Pages

65,536-/67,584-bytes

SECTOR 2 = 256 Pages

65,536-/67,584-bytes