Power-on/reset state, 1 initial power-up/reset timing restrictions, System considerations – Rainbow Electronics AT45DB081D User Manual

Page 31

31

3596N–DFLASH–11/2012

AT45DB081D

16. Power-on/Reset State

When power is first applied to the device, or when recovering from a reset condition, the device

will default to Mode 3. In addition, the output pin (SO) will be in a high impedance state, and a

high-to-low transition on the CS pin will be required to start a valid instruction. The mode (Mode

3 or Mode 0) will be automatically selected on every falling edge of CS by sampling the inactive

clock state.

16.1

Initial Power-up/Reset Timing Restrictions

At power up, the device must not be selected until the supply voltage reaches the V

CC

(min.) and

further delay of t

VCSL

. During power-up, the internal Power-on Reset circuitry keeps the device in

reset mode until the V

CC

rises above the Power-on Reset threshold value (V

POR

). At this time, all

operations are disabled and the device does not respond to any commands. After power up is

applied and the V

CC

is at the minimum operating voltage V

CC

(min.), the t

VCSL

delay is required

before the device can be selected in order to perform a read operation.

Similarly, the t

PUW

delay is required after the V

CC

rises above the Power-on Reset threshold

value (V

POR

) before the device can perform a write (Program or Erase) operation. After initial

power-up, the device will default in Standby mode.

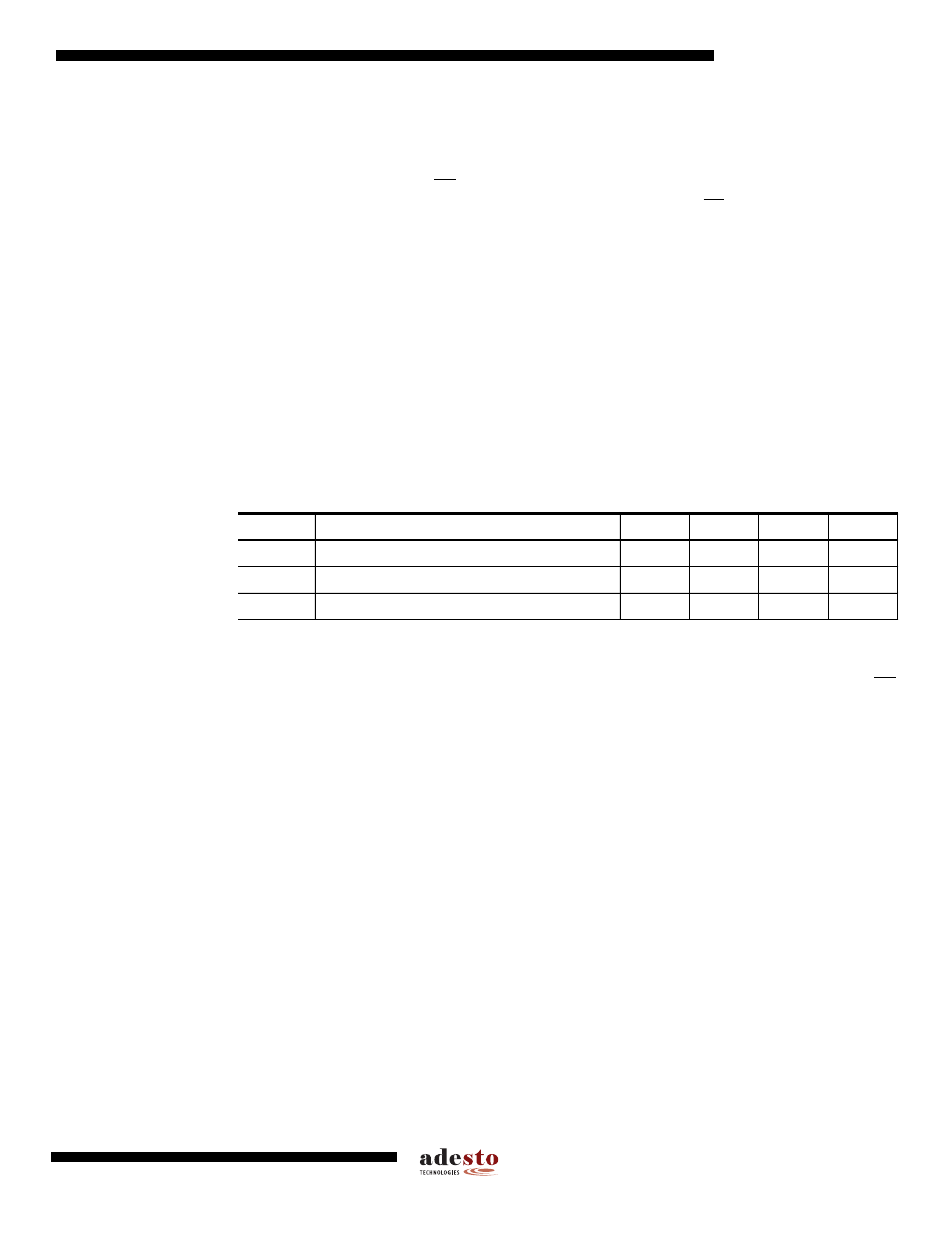

Table 16-1.

Initial Power-up/Reset Timing Restrictions

17. System Considerations

The RapidS serial interface is controlled by the clock SCK, serial input SI and chip select CS

pins. These signals must rise and fall monotonically and be free from noise. Excessive noise or

ringing on these pins can be misinterpreted as multiple edges and cause improper operation of

the device. The PC board traces must be kept to a minimum distance or appropriately termi-

nated to ensure proper operation. If necessary, decoupling capacitors can be added on these

pins to provide filtering against noise glitches.

As system complexity continues to increase, voltage regulation is becoming more important. A

key element of any voltage regulation scheme is its current sourcing capability. Like all Flash

memories, the peak current for DataFlash occur during the programming and erase operation.

The regulator needs to supply this peak current requirement. An under specified regulator can

cause current starvation. Besides increasing system noise, current starvation during program-

ming or erase can lead to improper operation and possible data corruption.

Symbol

Parameter

Min

Typ

Max

Units

t

VCSL

V

CC

(min.) to Chip Select low

70

µs

t

PUW

Power-Up Device Delay before Write Allowed

20

ms

V

POR

Power-ON Reset Voltage

1.5

2.5

V