Address registers and transfer status – Rainbow Electronics DS2422 User Manual

Page 25

DS2422

25 of 48

If there is a risk of unauthorized access to the DS2422 or manipulation of data, one should define passwords for

read access and full access. Before the passwords become effective, their use needs to be enabled. See Security

by Password for more details.

The last step to begin a mission is to issue the Start Mission command. As soon as it has received this command,

the DS2422 sets the MIP flag and clear the MEMCLR flag. With the immediate/delayed start mode (SUTA = 0),

after as many minutes as specified by the Mission Start Delay are over, the device wakes up, copy the current date

and time to the mission time stamp register, and log the first entry of the mission. This increments both the Mission

Samples Counter and Device Samples Counter. All subsequent log entries are made as specified by the value in

the Sample Rate Register and the EHSS bit.

If the Start Upon Temperature Alarm mode is chosen (SUTA = 1

,

ETL = 1) the DS2422 will first wait until the start

delay is over. Then the device wakes up in intervals as specified by the sample rate and EHSS bit and measure the

temperature. This increments the device samples counter only. Only after an alarming temperature is encountered

does the DS2422 set the mission time stamp. The first sample of the mission is logged one sample period after the

temperature alarm occurred.

From then on, both the Mission Samples Counter and Device Samples Counter

increments at the same time. All subsequent log entries are made as specified by the value in the Sample Rate

Register and the EHSS bit.

The general-purpose memory operates independently of the other memory sections and is not write-protected

during a mission. All memory of the DS2422 can be read at any time, e. g., to watch the progress of a mission.

Attempts to read the passwords will read 00h bytes instead of the data that is stored in the password registers.

ADDRESS REGISTERS AND TRANSFER STATUS

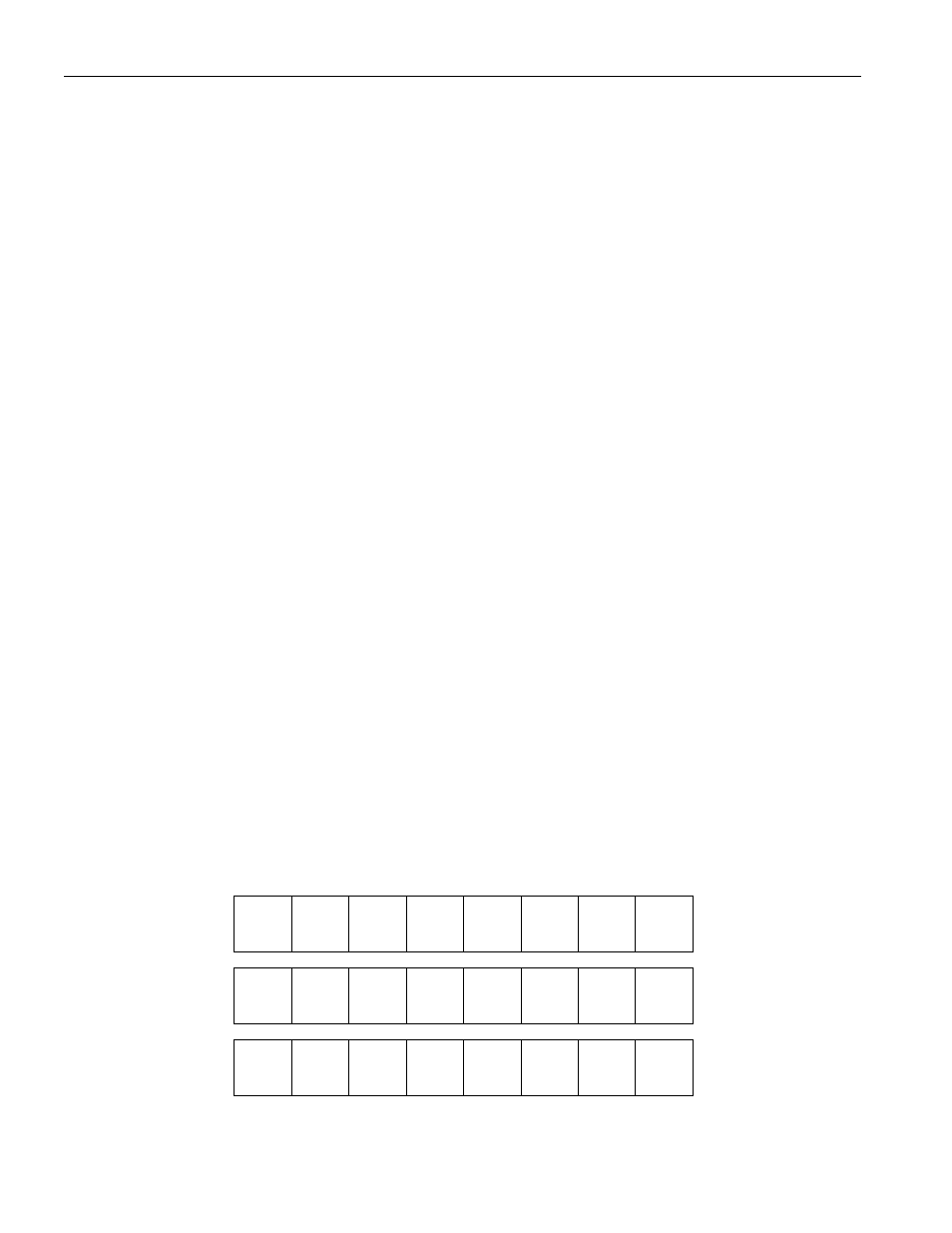

Because of the serial data transfer, the DS2422 employs three address registers, called TA1, TA2, and E/S (Figure

11). Registers TA1 and TA2 must be loaded with the target address to which the data is written or from which data

is sent to the master upon a Read command. Register E/S acts like a byte counter and transfer status register. It is

used to verify data integrity with Write commands. Therefore, the master only has read access to this register. The

lower 5 bits of the E/S Register indicate the address of the last byte that has been written to the scratchpad. This

address is called Ending Offset. The DS2422 requires that the Ending Offset is always 1Fh for a Copy

Scratchpad to function.

Bit 5 of the E/S Register, called PF or “partial byte flag,” is set if the number of data bits

sent by the master is not an integer multiple of 8. Bit 6 is always a 0. Note that the lowest 5 bits of the target

address also determine the address within the scratchpad, where intermediate storage of data will begin. This

address is called byte offset. If the target address for a Write command is 13Ch, for example, then the scratchpad

will store incoming data beginning at the byte offset 1Ch and will be full after only 4 bytes. The corresponding

ending offset in this example is 1Fh. For best economy of speed and efficiency, the target address for writing

should point to the beginning of a new page, i.e., the byte offset will be 0. Thus the full 32-byte capacity of the

scratchpad is available, resulting also in the ending offset of 1Fh. However, it is possible to write 1 or several

contiguous bytes somewhere within a page. The ending offset together with the Partial and Overflow Flag is mainly

a means to support the master checking the data integrity after a Write command. The highest valued bit of the E/S

Register, called AA or Authorization Accepted, indicates that a valid copy command for the scratchpad has been

received and executed. Writing data to the scratchpad clears this flag.

Figure 11. Address Registers

Bit #

7

6

5

4

3

2

1

0

Target Address (TA1)

T7

T6

T5

T4

T3

T2

T1

T0

Target Address (TA2)

T15

T14

T13

T12

T11

T10

T9

T8

Ending Address with

Data Status (E/S)

(Read Only)

AA

0

PF

E4

E3

E2

E1

E0