Real-time clock control – Rainbow Electronics DS2422 User Manual

Page 16

DS2422

16 of 48

Register Details

BIT DESCRIPTION

BIT(S)

DEFINITION

EDLA: Enable Data Low

Alarm

b0

This bit controls whether, during a mission, the Data Low Alarm Flag

DLF may be set, if a data value from the serial data interface is equal to

or lower than the value in the Data Low Alarm Threshold Register. If

EDLA is 1, data low alarms are enabled. If EDLA is 0, data low alarms

are not generated.

EDHA: Enable Data High

Alarm

b1

This bit controls whether, during a mission, the Data High Alarm Flag

DHF may be set, if a data value from the serial data interface is equal to

or higher than the value in the Data High Alarm Threshold Register. If

EDHA is 1, data high alarms are enabled. If EDHA is 0, data high

alarms are not generated.

REAL-TIME CLOCK CONTROL

To minimize the power consumption of a battery-operated datalogger, the RTC oscillator should be turned off when

device is not in use. The oscillator on/off bit is located in the RTC control register. This register also includes the

EHSS bit, which determines whether the sample rate is specified in seconds or minutes.

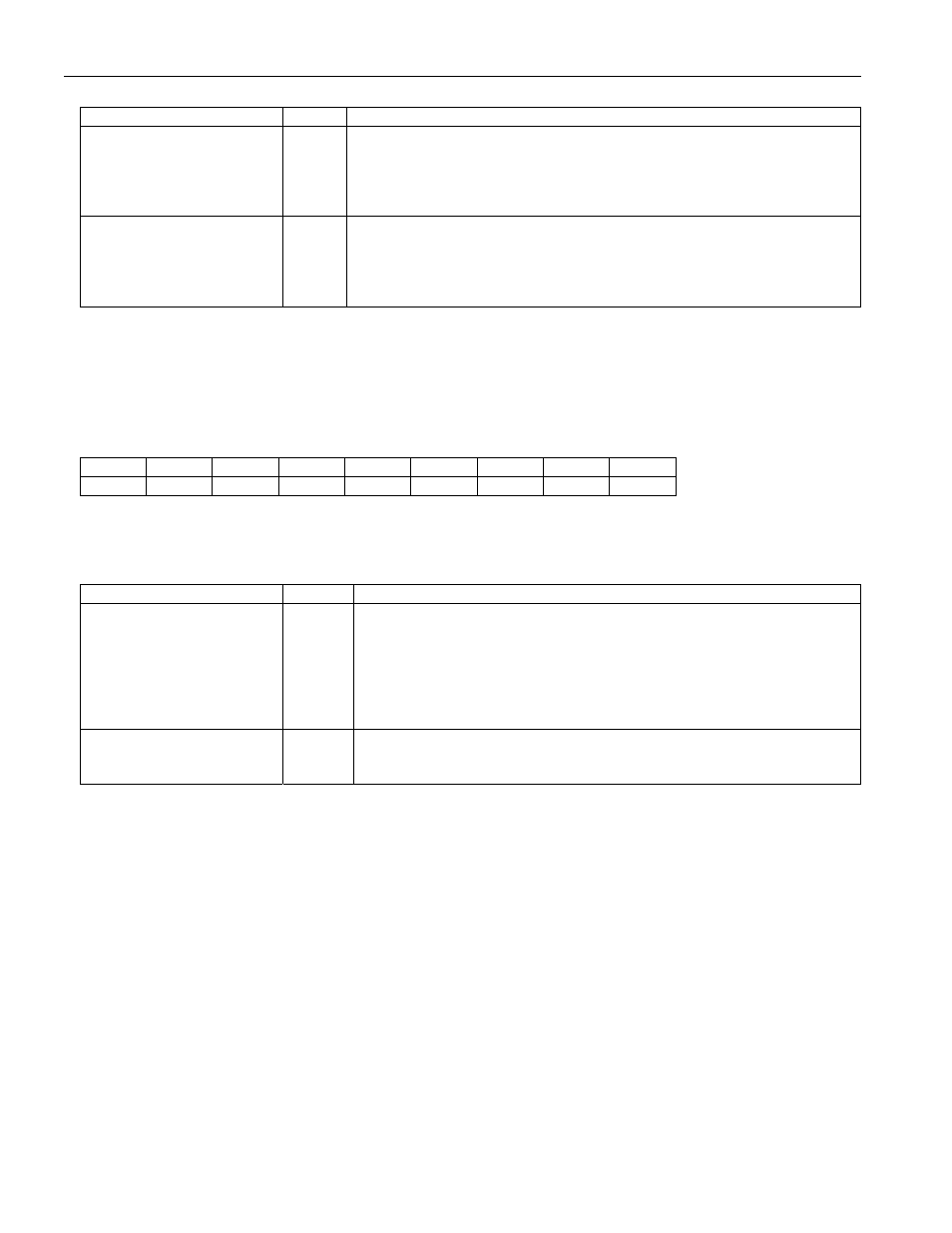

RTC Control Register Bitmap

ADDR

b7

b6

b5

b4

b3

b2

b1

b0

0212h

0

0

0

0

0

0

EHSS

EOSC

During a mission, there is only read access to this register. Bits 2-7 have no function. They always read 0 and

cannot be written to 1.

Register Details

BIT DESCRIPTION

BIT(S)

DEFINITION

EOSC: Enable Oscillator

b0

This bit controls the crystal oscillator of the RTC. When set to logic 1,

the oscillator will start operation. When written to logic 0, the oscillator

stops and the device is in a low-power data retention mode. This bit

must be 1 for normal operation. A temperature conversion or serial

data input must not be attempted while the RTC oscillator is stopped.

This will cause the device to enter into an undefined state, requiring a

power-on reset and restore of the trim settings to recover.

EHSS: Enable High Speed

Sample

b1

This bit controls the speed of the Sample Rate counter. When set to

logic 0, the sample rate is specified in minutes. When set to logic 1, the

sample rate is specified in seconds.