Multiplex clock, Global and local register addressing, Table 8. register address map – Rainbow Electronics MAX6963 User Manual

Page 15

MAX6960–MAX6963

4-Wire Serially Interfaced

8 x 8 Matrix Graphic LED Drivers

______________________________________________________________________________________

15

3-Wire Interface Data Lines

(ADDOUT and ADDIN)

One MAX6960 is designated the master device, and

this is allocated driver address 0. The master’s ADDIN

pin is connected to V+, identifying it as the first device.

This first MAX6960 should be the driver for the top-

left pixels of the display panel. The master’s

ADDOUT pin is connected to the second MAX6960’s

ADDIN pin, and that MAX6960’s ADDOUT pin is con-

nected to the third MAX6960’s ADDIN, and so on up to

256 MAX6960s. The last MAX6960’s ADDOUT pin is left

open circuit. The last MAX6960 should be the driver

for the bottom-right pixels of the display panel. The

ADDOUT is initialized low at the start of a 3-wire inter-

face configuration operation, and goes high (N + 1.5)

ADDCLK periods later, where n is the driver address of

the MAX6960 (0 to 255). See Figures 1 and 2 for con-

nection examples.

3-Wire Interface Clock (ADDCLK)

The ADDCLK pins for all MAX6960s are all connected

together. ADDCLK data rate is determined by OSC / 4,

nominally 1.048576 MHz. The ADDCLK pin for the mas-

ter MAX6960 (driver address 0) is always an output,

and all the other ADDCLKs are always inputs. ADDCLK

is active for exactly 256 clock cycles when a panel con-

figuration is being performed (on power-up reset, and

after a write to the global panel configuration register).

Use of ADDOUT as Plane Change Interrupt

(IRQ)

When the plane counter is configured to automatic

mode (bit 6 of the plane counter register is set) (Table

30), ADDOUT pulses low for a time of 512/OSC (nomi-

nally 122µs) at the start of every automatic plane

change. This signal can be used as an interrupt output

from the display panel to the host to flag that the previ-

ous display plane is now unused and can be written

with a new image.

Multiplex Clock

The OSC input for all MAX6960s sharing a 3-wire inter-

face bus (but not necessarily a 4-wire interface bus)

should be driven by a common CMOS-level clock rang-

ing between 1MHz and 8.5MHz. It is usually necessary

to use an external clock tree to fan out multiple clock

drives when larger numbers of MAX6960s are used

because of the capacitive loads. For example, each

one of the eight outputs of a standard 74HC541 octal

buffer could drive 8 to 32 MAX6960 OSC inputs,

depending on the layout used.

The recommended setting for OSC is 4.194303MHz.

This frequency sets the slow global plane counter reso-

lution to 1s, and the fast global plane counter resolution

to 1Hz.

Global and Local Register

Addressing

The register map (Table 8) contains three local regis-

ters and eight global registers. Global registers are

always written to in all MAX6960s (on the same 4-wire

interface) at the same time, using a 16-bit transmission.

A read from a global register also always results in a

read from driver address 0. The global nature of these

registers ensures that all drivers work together, and

there is no chance of a software miss-send causing, for

example, multiple MAX6960s to try to transmit on the 4-

wire DOUT line at the same time.

The three local registers can be written to on an individ-

ual basis (updates just the MAX6960 indirected by the

global driver indirect address register), or on a global

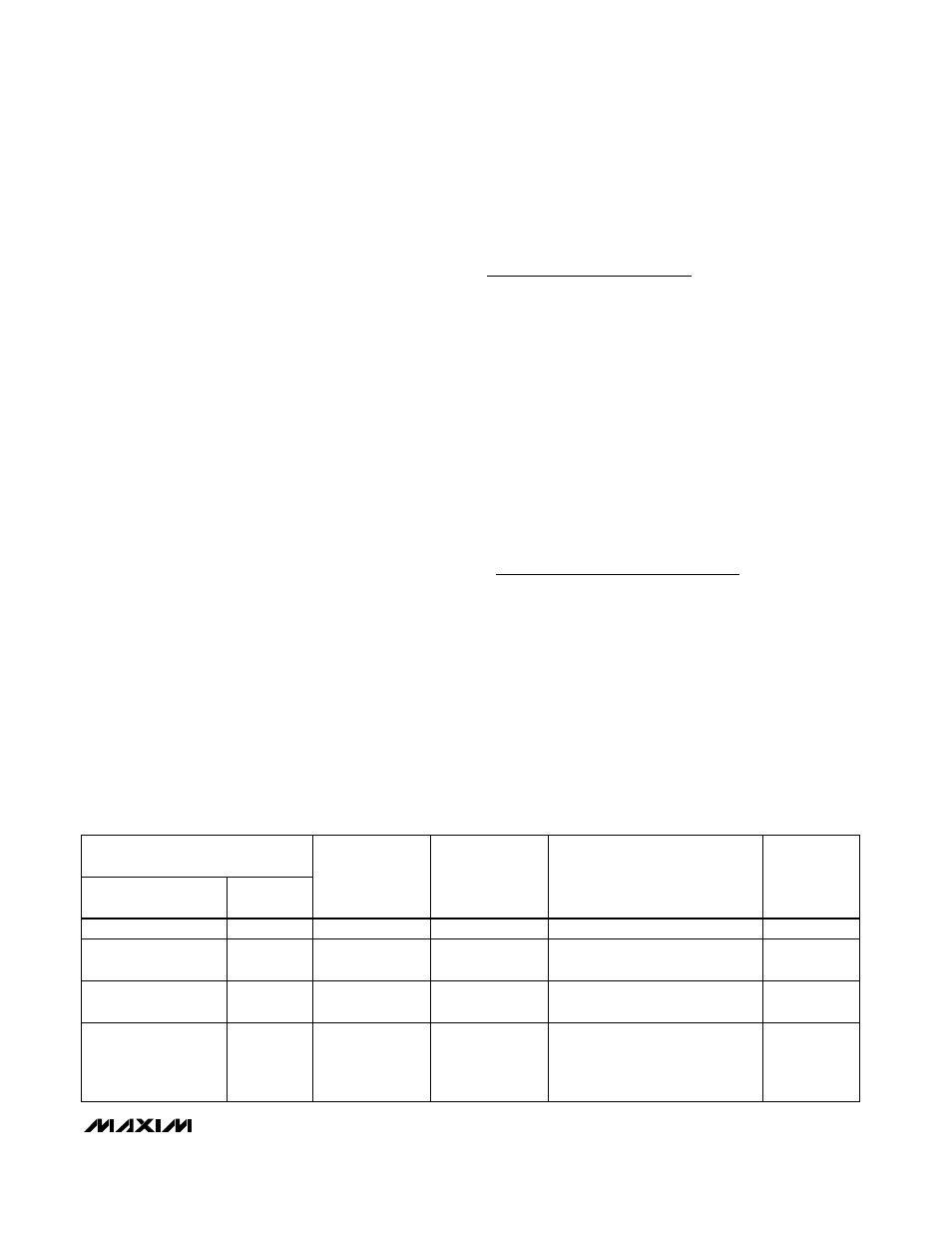

GLOBAL PANEL CONFIGURATION

REGISTER

PLANES/INTENSITY

(PI BIT)

COLOR

(C BIT)

PIXEL-LEVEL

INTENSITY

CONTROL

DISPLAY TYPE

DISPLAY MAPPING

ADDRESSES PER PLANE

DISPLAY

PLANES

AVAILABLE

0

0

1 bit per pixel

Monocolor

16 red contiguous

4

0

1

1 bit per pixel

RGY

8 red contiguous,

8 green contiguous

4

1

0

2 bits per pixel

Monocolor

16 red contiguous,

16 red contiguous

2

1

1

2 bits per pixel

RGY

16 red

(2 noncontiguous groups of 8),

16 green

(2 noncontiguous groups of 8)

2

Table 8. Register Address Map