Table 7. register addressing modes – Rainbow Electronics MAX6963 User Manual

Page 11

MAX6960–MAX6963

4-Wire Serially Interfaced

8 x 8 Matrix Graphic LED Drivers

______________________________________________________________________________________

11

8-Bit Transmissions

Eight-bit transmissions are write-only, data-only

accesses that write data to the display memory indi-

rected by the global display indirect address register

(Figure 6). The global display indirect address register

autoincrements after the write access. Eight-bit trans-

missions provide the quickest method of updating a

plane of display memory of the MAX6960. It is the most

suitable display update method if the host system

builds an image in local memory, and then dumps the

image into a display plane of the MAX6960.

16-Bit Transmissions

Sixteen-bit transmissions are read/write, command-

and-data accesses to the MAX6960’s configuration

registers (Figure 7). A write can generally be global

(updates all MAX6960s on the 4-wire bus with the same

data) or specific (updates just the MAX6960 indirected

by the global driver indirect address register). Note:

The global driver indirect address register selects a

specific MAX6960. This is not the same as the glob-

al display indirect address register, which points to

display memory that could be in any MAX6960. A

16-bit read is always indirected through the global dri-

ver indirect address register to select only one

MAX6960 to respond. When a read or write is indirect-

ed through the global driver indirect address register,

the 16-bit command can choose whether the global dri-

ver indirect address is autoincremented after the com-

mand has been executed. This allows the host to set up

one or more registers in consecutive MAX6960s with

the display indirect address, autoincrementing only

when required.

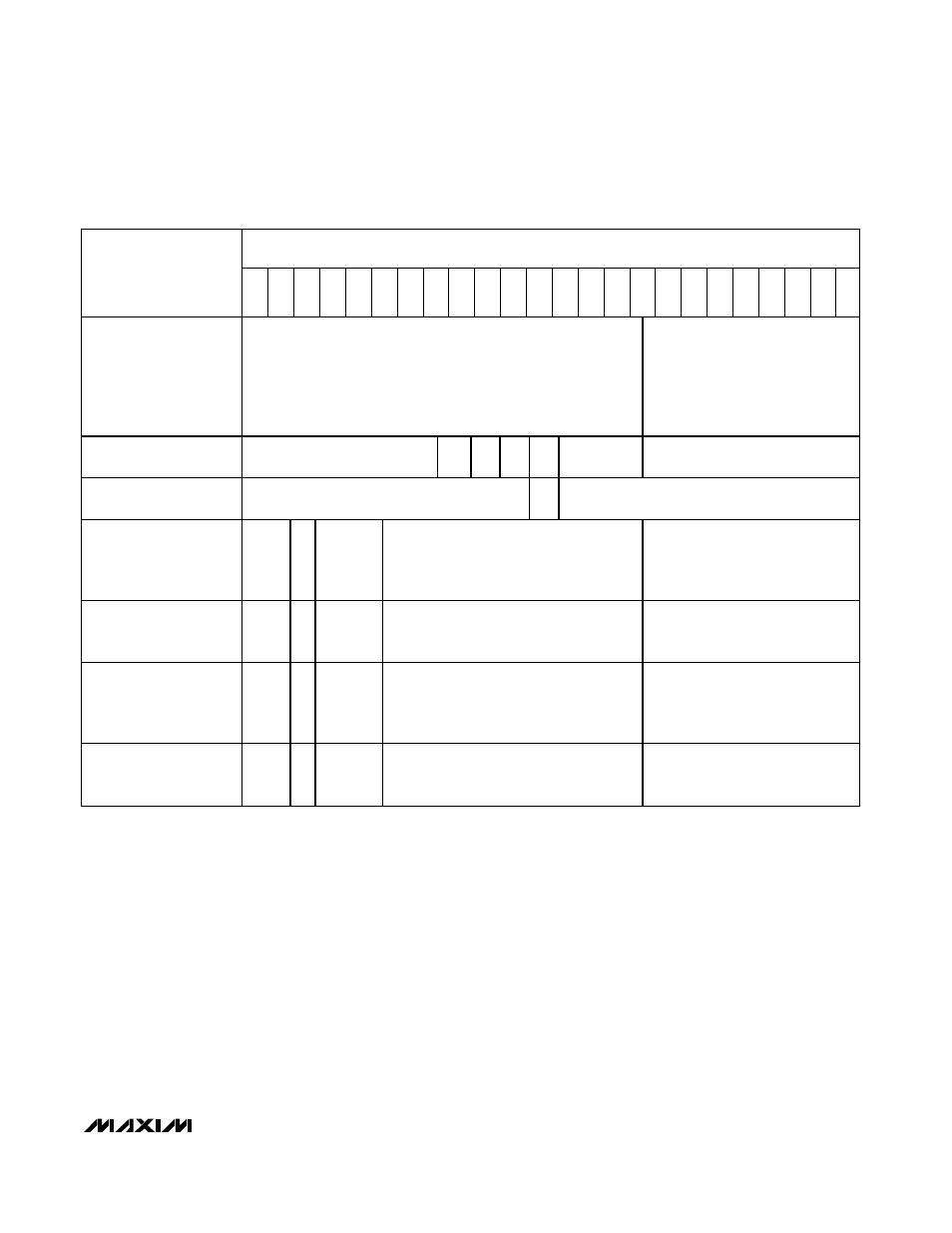

8-, 16-, OR 24-BIT DATA PACKET SENT TO MAX6960

DATA FORMAT

D23

D22

D21

D20

D19

D18

D17

D16

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

8-bit indirect display

memory addressing.

Address is global display

indirect address (14 bits)

stored as {MSB, LSB} in

{register 0x0A, register

0x09}.

—

8 bits of display memory

16-bit device addressing.

—

R/

W AI L/G

0

4-bit

address

8 bits of driver register data

Factory reserved; do not

write to this address.

—

1

—

24-bit direct display

memory addressing

(monocolor 1 bit per

pixel).

R/

W

X

Planes

0, 1, 2, 3

12-bit addressing across 256 drivers,

4096 x 8 red pixels

8 bits of display memory

(1 bit per pixel)

24-bit direct display

memory addressing

(RGY 1 bit per pixel).

R/

W

X

Planes

0, 1, 2, 3

12-bit addressing across 256 drivers,

2048 x 8 red pixels, and

2048 x 8 green pixels

8 bits of display memory

(1 bit per pixel)

24-bit direct display

memory addressing

(monocolor 2 bits per

pixel).

R/

W

X

Planes

0, 1

13-bit addressing across 256 drivers,

4096 x 4 red pixels

8 bits of display memory

(2 bits per pixel)

24-bit direct display

memory addressing

(RGY 2 bits per pixel).

R/

W

X

Planes

0, 1

13-bit addressing across 256 drivers,

4096 x 4 red pixels, and

4096 x 4 green pixels

8 bits of display memory

(2 bits per pixel)

Table 7. Register Addressing Modes