Table 7. s sk kiip p settings – Rainbow Electronics MAX8760 User Manual

Page 28

MAX8760

Dual-Phase, Quick-PWM Controller for AMD

Mobile Turion 64 CPU Core Power Supplies

28

______________________________________________________________________________________

Together, the feedback-sense resistor (R

FBS

) and

GNDS input sum the remote-sense voltages with the

feedback signals that set the voltage-positioned output,

enabling true differential remote sense of the processor

voltage. Connect the feedback-sense resistor (R

FBS

)

and ground-sense input (GNDS) directly to the proces-

sor’s core supply remote-sense outputs as shown in the

Standard Applications Circuit.

Offset Amplifier

The multiphase quick-PWM controllers include a third

amplifier used to add small offsets to the voltage-posi-

tioned load line. The offset amplifier is summed directly

with the feedback voltage, making the offset gain inde-

pendent of the DAC code. This amplifier has the ability

to offset the output by ±100mV.

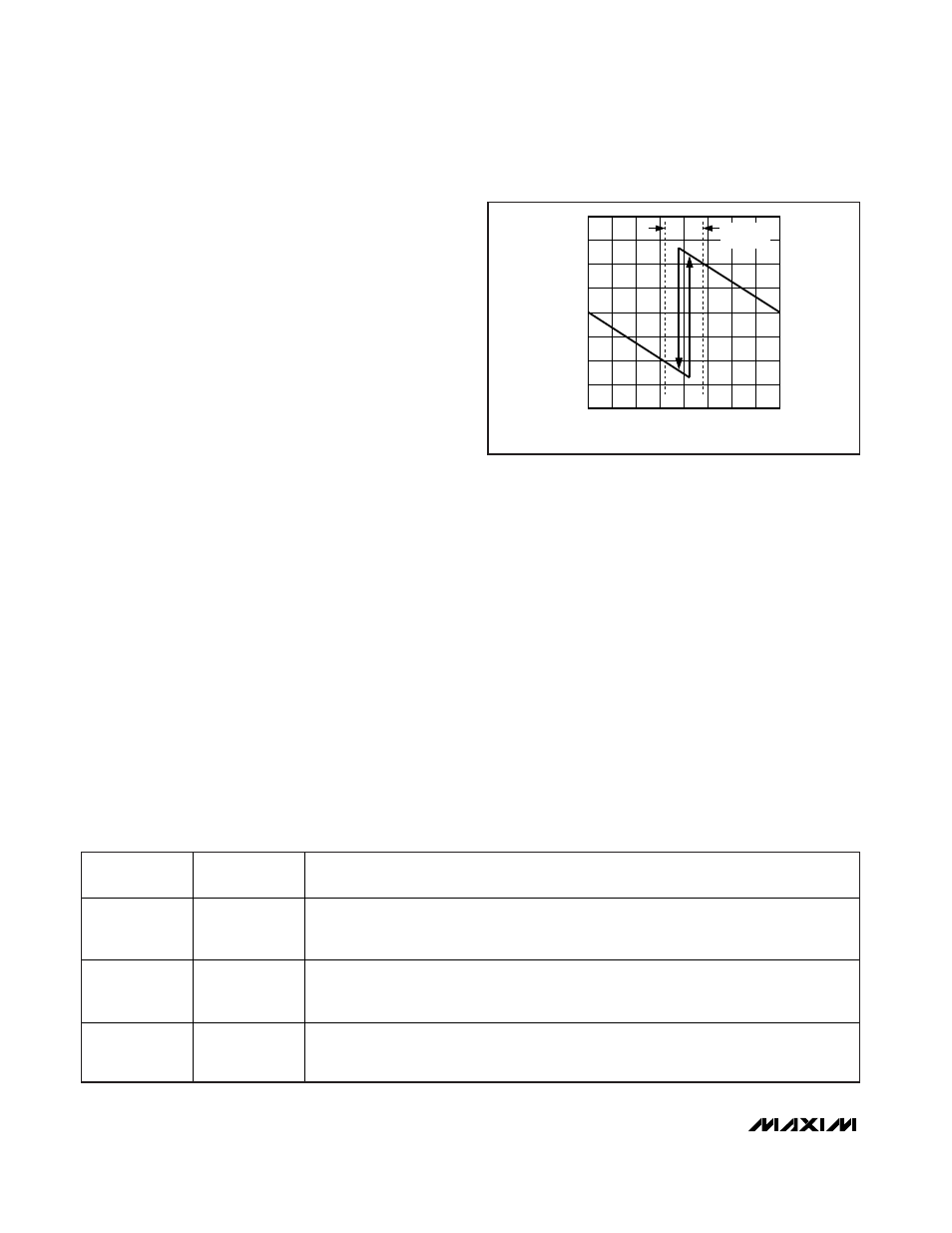

The offset is adjusted using resistive voltage-dividers at

the OFS input. For inputs from 0 to 0.8V, the offset

amplifier adds a negative offset to the output that is

equal to 1/8 the voltage appearing at the selected OFS

input (V

OUT

= V

DAC

- 0.125 x V

OFS

). For inputs from

1.2V to 2V, the offset amplifier adds a positive offset to

the output that is equal to 1/8th the difference between

the reference voltage and the voltage appearing at the

selected OFS input (V

OUT

= V

DAC

+ 0.125 x (V

REF

-

V

OFS

)). With this scheme, the controller supports both

positive and negative offsets with a single input. The

piecewise linear transfer function is shown in the

Typical Operating Characteristics. The regions of the

transfer function below zero, above 2V, and between

0.8V and 1.2V are undefined. OFS inputs are disal-

lowed in these regions, and the respective effects on

the output are not specified.

The controller disables the offset amplifier during sus-

pend mode (SUS = REF or high).

Forced-PWM Operation (Normal Mode)

During normal mode, when the CPU is actively running

(SKIP = high, Table 7), the quick-PWM controller oper-

ates with the low-noise forced-PWM control scheme.

Forced-PWM operation disables the zero-crossing

comparator, forcing the low-side gate-drive waveform

to be constantly the complement of the high-side gate-

drive waveform. This keeps the switching frequency

fairly constant and allows the inductor current to

reverse under light loads, providing fast, accurate neg-

ative output voltage transitions by quickly discharging

the output capacitors.

Forced-PWM operation comes at a cost: the no-load 5V

bias supply current remains between 10mA to 60mA

per phase, depending on the external MOSFETs and

switching frequency. To maintain high efficiency under

light-load conditions, the processor may switch the

controller to a low-power pulse-skipping control

scheme after entering suspend mode.

Table 7.

S

SK

KIIP

P Settings*

SKIP

CONNECTION

MODE

OPERATION

High

(3.3V or V

CC

)

Two-phase

forced PWM

The controller operates with a constant switching frequency, providing low-noise forced-PWM

operation. The controller disables the zero-crossing comparators, forcing the low-side gate-

drive waveform to be constantly the complement of the high-side gate-drive waveform.

REF

Two-phase

pulse skipping

The controller automatically switches over to PFM operation under light loads. The controller

keeps both phases active and uses the automatic pulse-skipping control scheme, alternating

between the primary and secondary phases with each cycle.

GND

One-phase

pulse skipping

The controller automatically switches over to PFM operation under light loads. Only the main

phase is active. The secondary phase is disabled, DLS and DHS are pulled low, so LXS is

high impedance.

*Settings for a dual 180° out-of-phase controller.

-200

-100

0

100

200

0

1.0

0.5

0.8

1.2

1.5

2.0

OFS VOLTAGE (V)

OUTPUT OFFSET VOLTAGE (mV)

UNDEFINED

REGION

Figure 6. Offset Voltage