1 introduction to the hpi, Host port interface (hpi), User's guide – Texas Instruments TMS320C6457 User Manual

Page 7: 1introduction to the hpi

HPID

R/W FIFOs

HPIA

Increment

HPIC

Access

type

HD[31:0]/HD[15:0]

HDS1, HDS2

HR/W

HAS

HCNTL0

HCNTL1

(optional)

HINT

HRDY

HPI

Host

Data

Address

ALE

R/W

IRQ

Ready

HCS

Chip select

DSP

HPI DMA

logic

HHWIL

(if needed)

Data strobes

Switched

central

resource

C64x+

megamodule

External

memory

I/F

Other

peripherals

EDMA3

Internal

memory

User's Guide

SPRUGK7A – March 2009 – Revised July 2010

Host Port Interface (HPI)

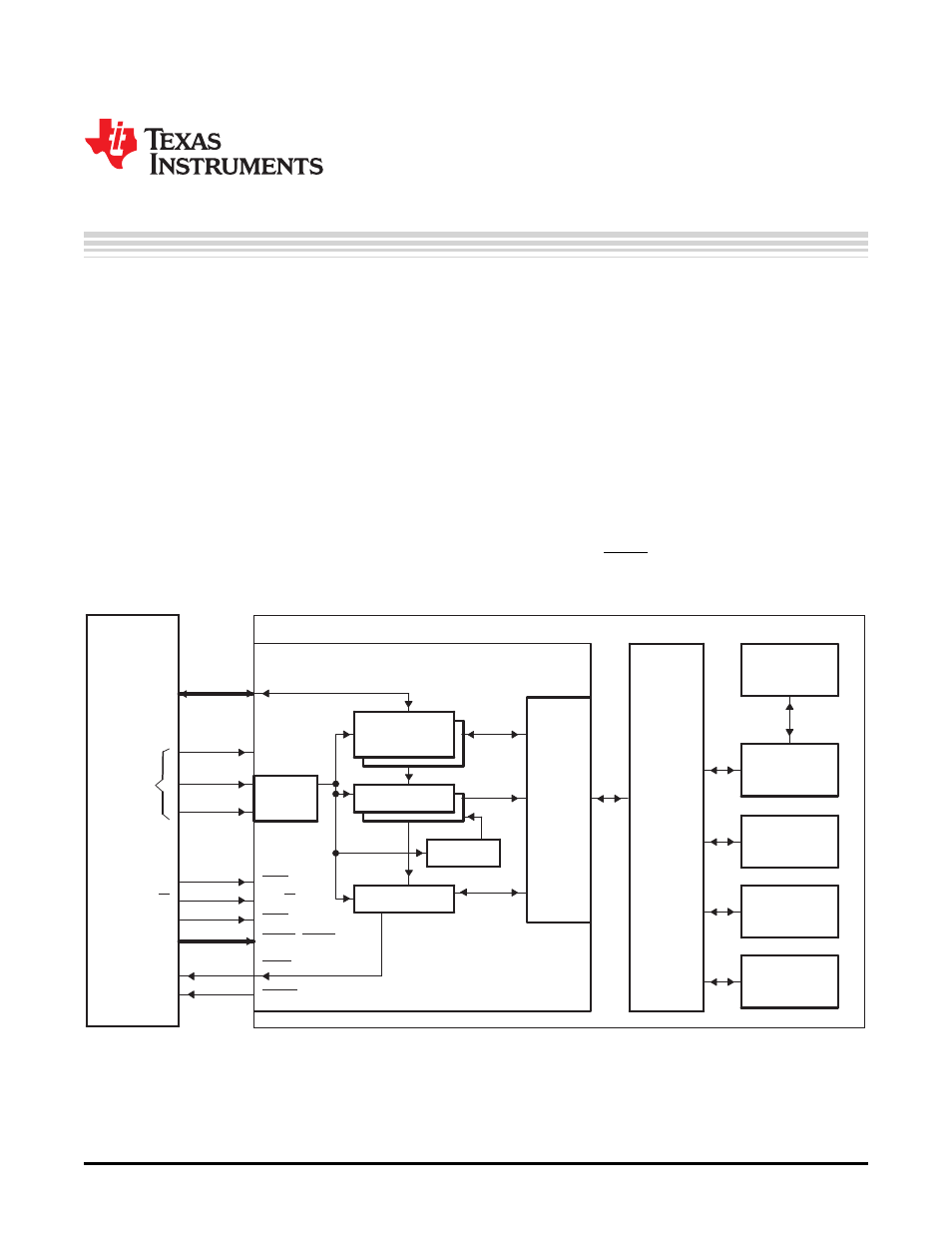

This guide describes the host port interface (HPI) on the TMS320C6457 digital signal processors (DSPs).

The HPI enables an external host processor (host) to directly access DSP resources (including internal

and external memory) using a 16-bit (HPI16) or 32-bit (HPI32) interface.

1

Introduction to the HPI

The HPI provides a parallel port interface through which an external host processor (host) can access

DSP resources. The HPI enables a host device and CPU to exchange information via internal or external

memory. Dedicated address and data registers (HPIA and HPID respectively) within the HPI provide the

data path between the external host interface and the processor resources. An HPI control register (HPIC)

is available to the host and the CPU for various configuration and interrupt functions.

is a high-level block diagram showing how the HPI connects a host (left side of figure) and the

DSP internal resources (right side of figure). The host functions as a master to the HPI. Host activity is

asynchronous to the internal clock that drives the HPI. When HPI resources are temporarily busy or

unavailable, the HPI informs the host by deasserting the HPI-ready (HRDY) output signal.

Figure 1. HPI Position in the Host-DSP System

7

SPRUGK7A – March 2009 – Revised July 2010

Host Port Interface (HPI)

Copyright © 2009–2010, Texas Instruments Incorporated