Figure 27 – Texas Instruments TMS320C6457 User Manual

Page 31

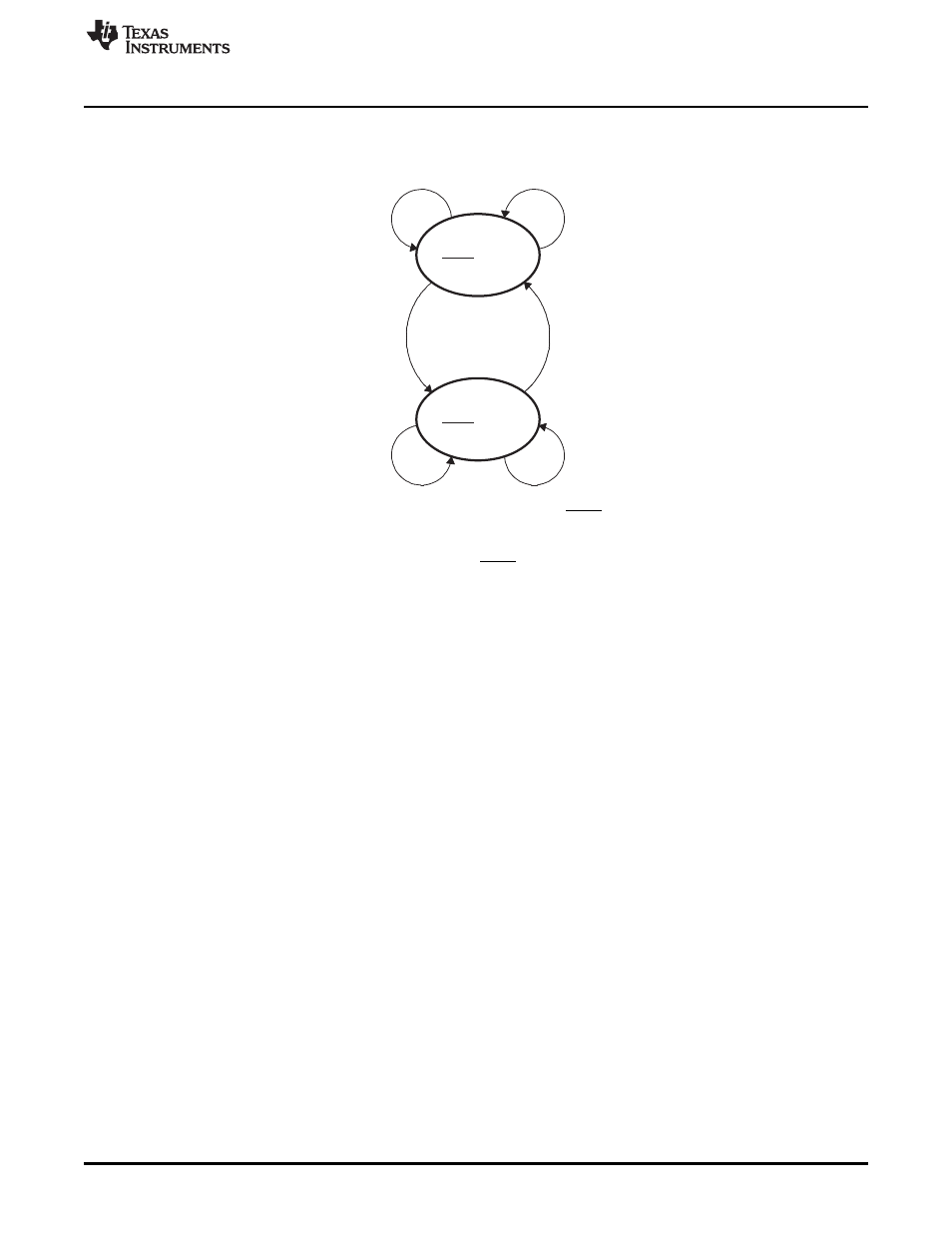

HINT bit=0

HINT signal

is high

is low

HINT signal

HINT bit=1

CPU writes 1

to HINT bit

Host writes 1

to HINT bit

Interrupt

active

CPU writes 0

to HINT bit

No interrupt/

interrupt

cleared

Host writes 0 or 1

to HINT bit

CPU writes 0 or 1

to HINT bit

Host writes 0

to HINT bit

www.ti.com

Interrupts Between the Host and the CPU

Figure 27. CPU-to-Host Interrupt State Diagram

If the CPU writes 1 to the HINT bit of HPIC, the HPI drives the HINT signal low, indicating an interrupt

condition to the host. Before the CPU can use the HINT bit to generate a subsequent interrupt to host, the

host must acknowledge the current interrupt by writing 1 to the HINT bit. When the host does this, the HPI

clears the HINT bit (HINT = 0), and this drives the HINT signal high. The CPU should read HPIC and

ensure HINT = 0 before generating subsequent interrupts. Writes of 0 have no effect on the HINT bit. A

hardware reset immediately clears the HINT bit and thus clears an active CPU-to-host interrupt.

31

SPRUGK7A – March 2009 – Revised July 2010

Host Port Interface (HPI)

Copyright © 2009–2010, Texas Instruments Incorporated