Texas Instruments TMS320C6457 User Manual

Page 10

Introduction to the HPI

www.ti.com

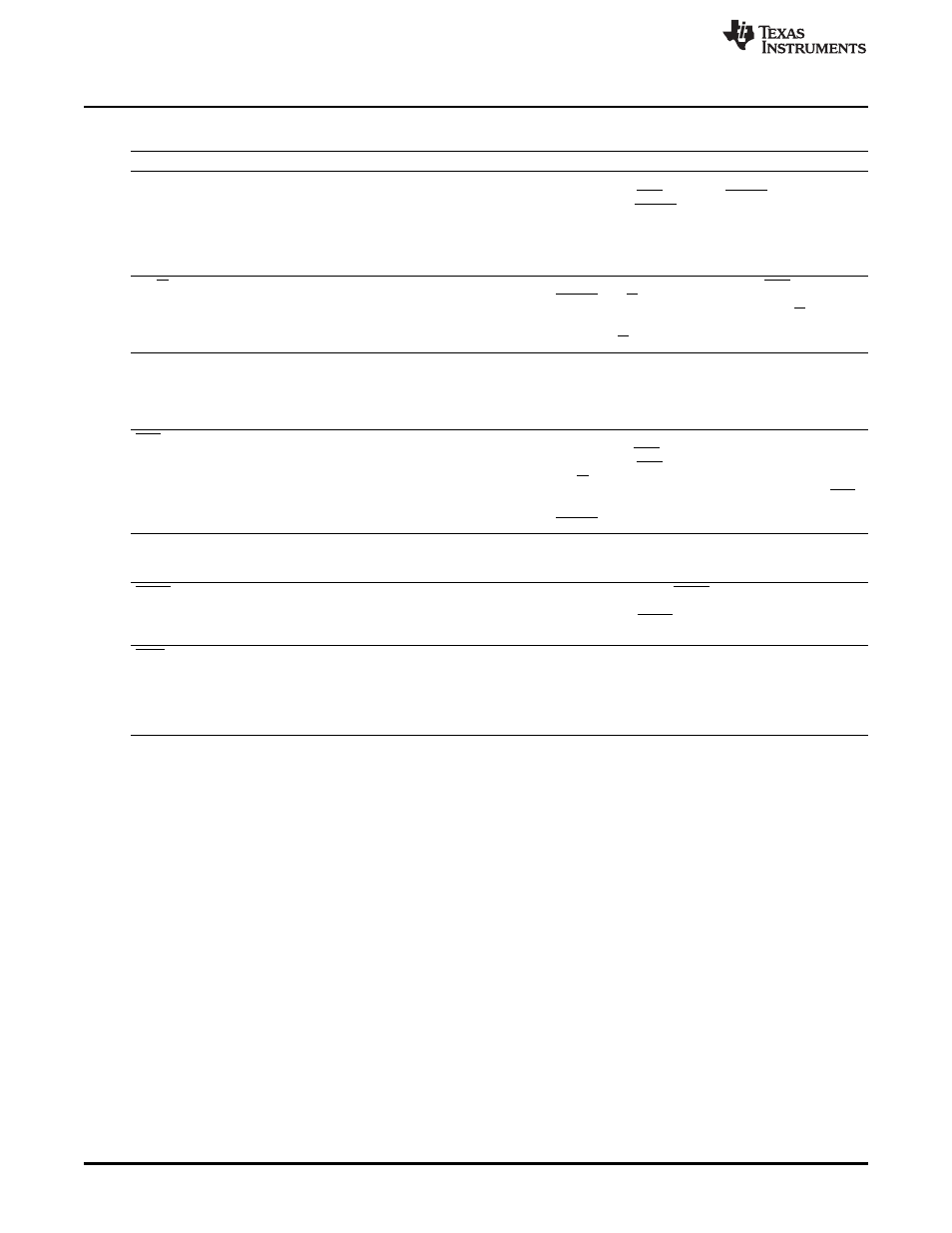

Table 2. HPI Signals (continued)

Signal

State

(1)

Host Connection

Description

HCNTL[1:0]

I

Address or control pins

The HPI latches the logic levels of these pins on the

falling edge of HAS or internal HSTRB (for details

about internal HSTRB, see

). The four

binary states of these pins determine the access type

of the current transfer (HPIC, HPID with

autoincrementing, HPIA, or HPID without

autoincrementing).

HR/W

I

R/W strobe pin

HPI read/write. On the falling edge of HAS or internal

HSTRB, HR/W indicates whether the current access is

to be a read or write operation. Driving HR/W high

indicates the transfer is a read from the HPI, while

driving HR/W low indicates a write to the HPI.

HHWIL

I

Address or control pins

Halfword identification control input. This bit identifies

the first and second halfwords of a dual halfword cycle

operation. HHWIL=0 identifies the first cycle and

HHWIL=1 identifies the second cycle. HHWIL applies

only to HPI16 mode and not to HPI32 mode.

HAS

I

ALE (address latch enable) or

Address strobe. A host with a multiplexed address/data

address strobe pin

bus can have HAS connected to its ALE pin. The

falling edge of HAS latches the logic levels of the

HR/W, HCNTL1, and HCNTL0 pins, which are typically

connected to host address lines. When used, the HAS

signal must precede the falling edge of the internal

HSTRB signal.

HD[31:0]

I/O/Z

Data bus

The HPI data bus carries the data to/from the HPI.

HD[15:0]

HD[31:0] applies to HPI32 and HD[15:0] applies to

HPI16.

HRDY

O/Z

Asynchronous ready pin

When the HPI drives HRDY low, the host has

permission to complete the current host cycle. When

the HPI drives HRDY high, the HPI is not ready for the

current host cycle to complete.

HINT

O/Z

Interrupt pin

The DSP can interrupt the host processor by writing a

1 to the HINT bit of HPIC. Before subsequent HINT

interrupts can occur, the host must clear previous

interrupts by writing a 1 to the HINT bit. This pin is

active-low and inverted from the HINT bit value in

HPIC.

10

Host Port Interface (HPI)

SPRUGK7A – March 2009 – Revised July 2010

Copyright © 2009–2010, Texas Instruments Incorporated