3 hpi operation, 1 host-hpi signal connections – Texas Instruments TMS320C6457 User Manual

Page 12

Address or I/O

Read/Write

Chip select

Data strobe

A

Data/address

Interrupt

Ready

HCNTL[1:0]

HR/W

HCS

HDS1

HDS2

HD[31:0]

HINT

HRDY

HPI

Host

Address latch enable

HAS

No connect

HHWIL

Logic high

2

32

DSP

HPI Operation

www.ti.com

3

HPI Operation

3.1

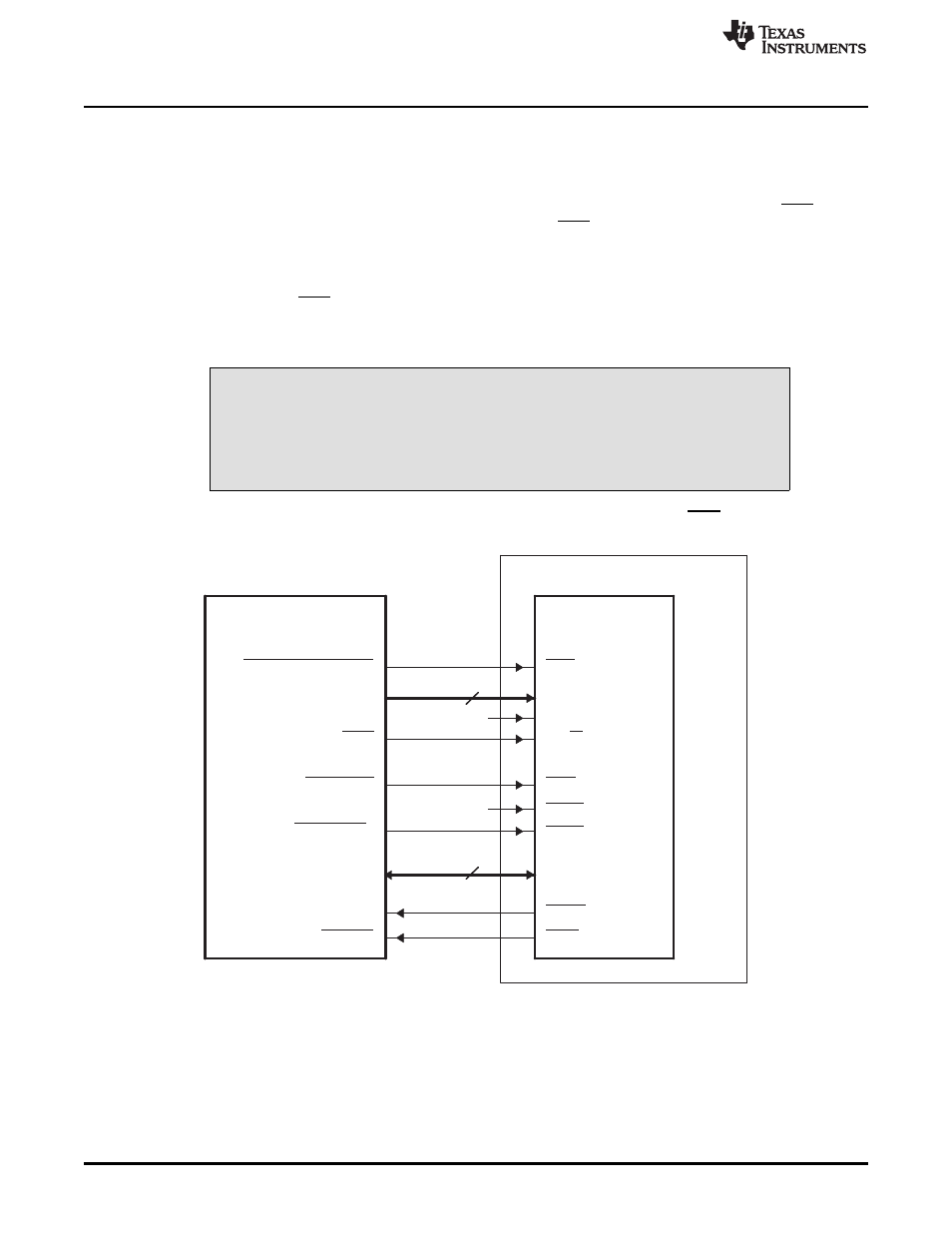

Host-HPI Signal Connections

and

show examples of signal connections for the 32-bit multiplexed mode.

and

show similar examples for the 16-bit multiplexed mode. In

and

, the HAS signal

is used as described in

. In

and

, HAS is tied high (not used). Note the

following key comparisons between the signal connections in the two interface modes:

•

The HPI_WIDTH configuration pin of the DSP must be held high at reset for the 32-bit multiplexed

mode (HPI32) or low at reset for the 16-bit multiplexed mode (HPI16).

•

The address strobe (HAS) of the HPI is optional for both modes.

•

The halfword identification control line (HHWIL) of the HPI is not used in the 32-bit multiplexed mode,

but is required in the 16-bit multiplexed mode.

CAUTION

Note that the encoding of HCNTL0 and HCNTL1 for the different types of HPI

accesses varies on many TI DSPs; therefore, you should use caution to ensure

that the correct encoding of these inputs is used for your device. The encoding

of these signals as described in this document applies only to C6457 DSPs.

Figure 2. Example of Host-DSP Signal Connections When Using the HAS Signal

in the 32-Bit Multiplexed Mode

A

Data strobing options are given in

12

Host Port Interface (HPI)

SPRUGK7A – March 2009 – Revised July 2010

Copyright © 2009–2010, Texas Instruments Incorporated