Texas Instruments TMS320C6457 User Manual

Page 23

1st halfword

00 or 10

00 or 10

2nd halfword

Internal

HD[15:0]

HRDY

HHWIL

HR/W

HCNTL[1:0]

HCS

HSTRB

HCS

HCNTL[1:0]

HR/W

HHWIL

Internal

HSTRB

HD[15:0]

HRDY

1st halfword

2nd halfword

1st halfword

2nd halfword

11

11

10

10

HPIA write

HPID read

HCS

Internal

HRDY

HD[15:0]

HR/W

HCNTL[1:0]

HHWIL

10

10

01

01

01

1st halfword

2nd halfword

1st halfword

2nd halfword

1st halfword

HSTRB

HPIA write

HPID+ reads

www.ti.com

HPI Operation

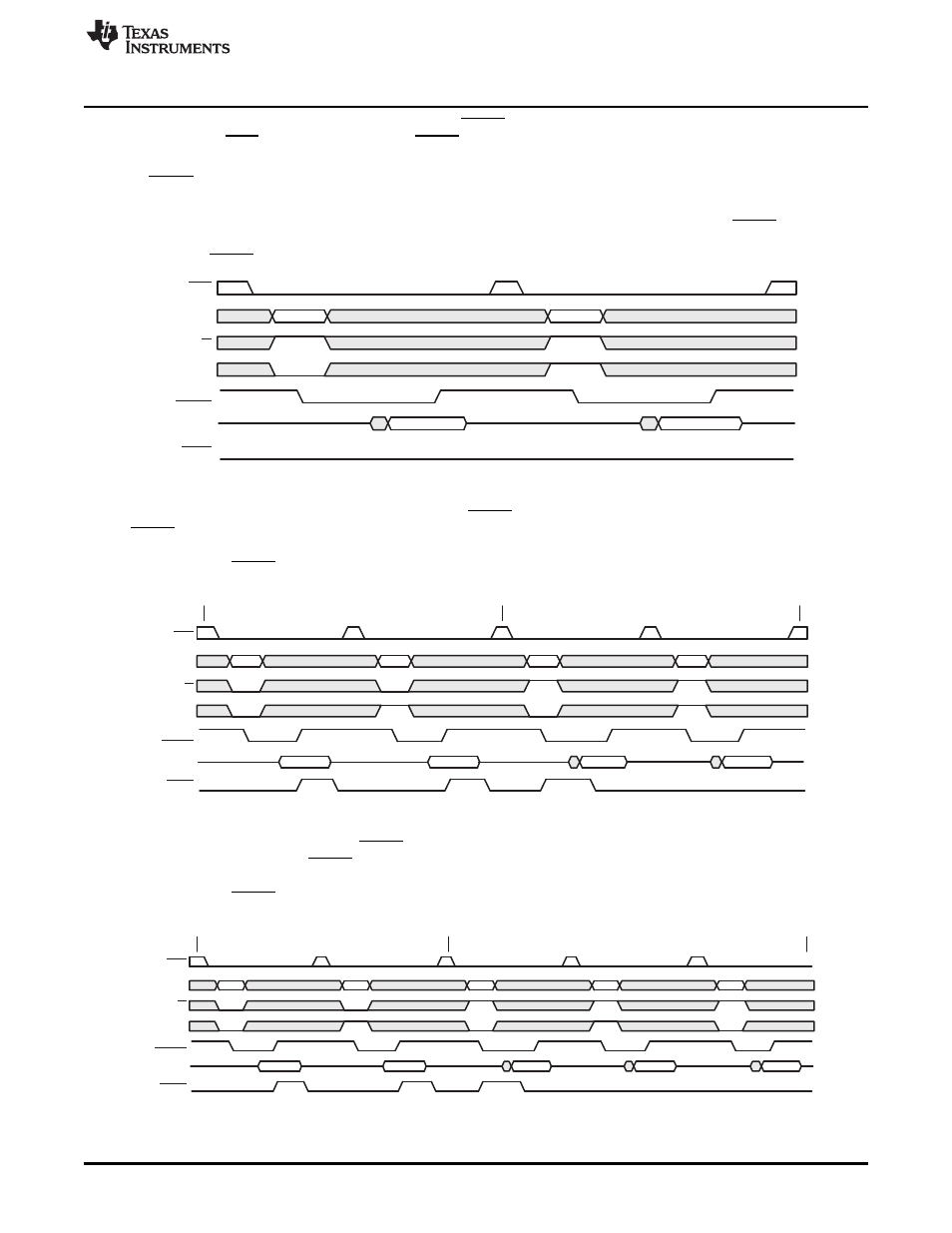

The following sections describe the behavior of HRDY during HPI register accesses. In all cases, the chip

select signal, HCS, must be asserted for HRDY to go high.

3.9.1

HRDY Behavior During 16-Bit Multiplexed Read Operations

shows an HPIC (HCNTL[1:0] = 00b) or HPIA (HCNTL[1:0] = 10b) read cycle during 16-bit

multiplexed HPI operation. Neither an HPIC read cycle nor an HPIA read cycle causes HRDY to go high.

Figure 12. HRDY Behavior During an HPIC or HPIA Read Cycle in the 16-Bit Multiplexed Mode

includes an HPID read cycle without autoincrementing in the 16-bit multiplexed mode. The host

writes the memory address during the HPIA (HCNTL[1:0] = 10b) write cycle, and the host reads the data

during the HPID (HCNTL[1:0] = 11b) read cycle. HRDY goes high for each HPIA halfword access, but

HRDY goes high for only the first halfword access in each HPID read cycle.

Figure 13. HRDY Behavior During a Data Read Operation in the 16-Bit Multiplexed Mode

(Case 1: HPIA Write Cycle Followed by Nonautoincrement HPID Read Cycle)

includes an autoincrement HPID read cycle in the 16-bit multiplexed mode. The host writes the

memory address while asserting HCNTL[1:0] = 10b and reads the data while asserting HCNTL[1:0] = 01b.

During the first HPID read cycle, HRDY goes high for only the first halfword access, and subsequent HPID

read cycles do not cause HRDY to go high.

Figure 14. HRDY Behavior During a Data Read Operation in the 16-Bit Multiplexed Mode

(Case 2: HPIA Write Cycle Followed by Autoincrement HPID Read Cycles)

23

SPRUGK7A – March 2009 – Revised July 2010

Host Port Interface (HPI)

Copyright © 2009–2010, Texas Instruments Incorporated