6 fifos and bursting, 1 read bursting, Section 6 – Texas Instruments TMS320C6457 User Manual

Page 32

Write FIFO

control logic

Host write

pointer

HPI DMA

read pointer

Write FIFO

Host

writes

Read FIFO

reads

Host

control logic

Read FIFO

Host read

pointer

HPI DMA

write pointer

HPI

DMA

logic

Switched

central

Burst

writes

reads

Burst

resource

DSP

internal/

external

memory

FIFOs and Bursting

www.ti.com

6

FIFOs and Bursting

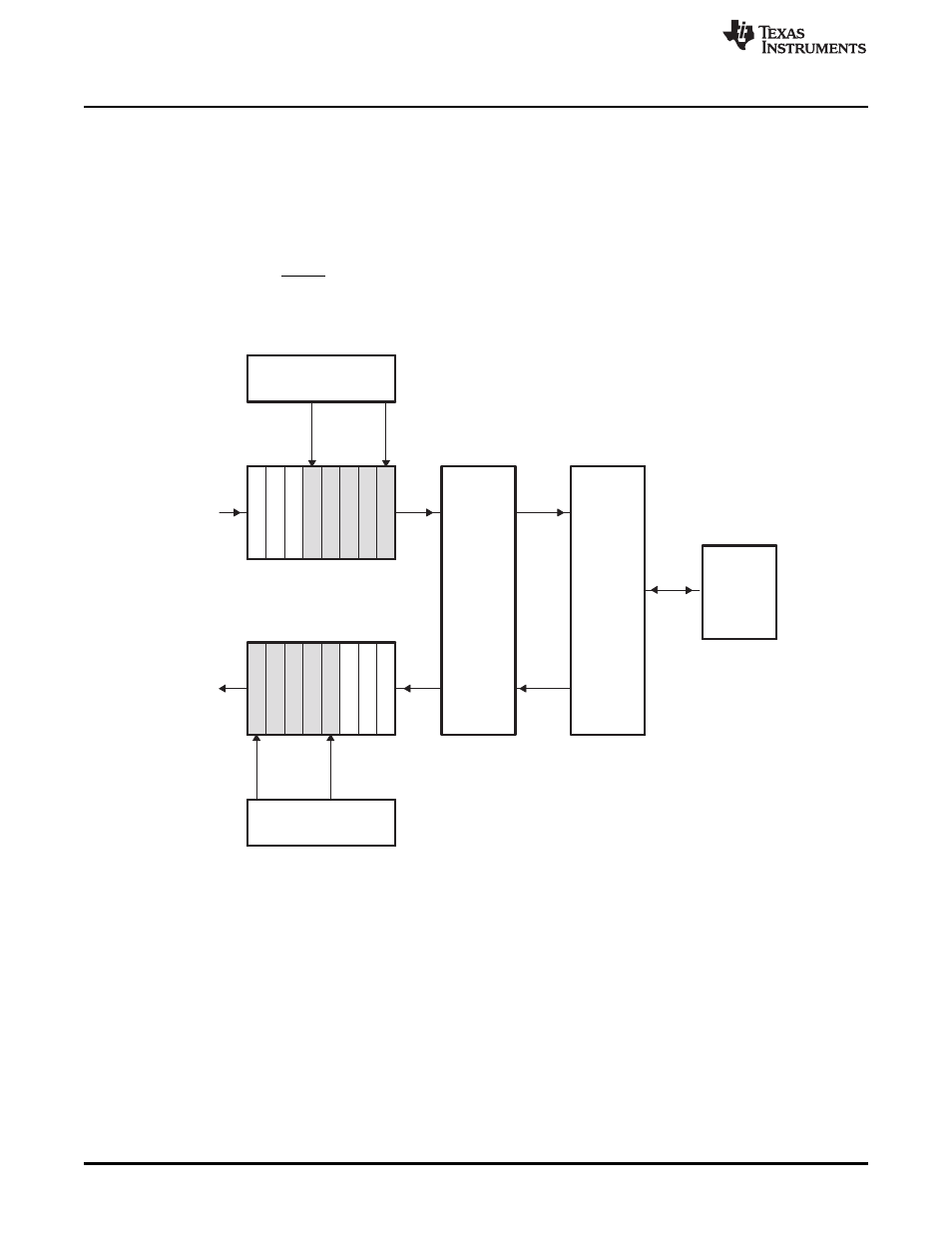

The HPI data register (HPID) is a port through which the host accesses two first-in, first-out buffers

(FIFOs). As shown in

, a read FIFO supports host read cycles, and a write FIFO supports host

write cycles. Both read and write FIFOs are 8-words deep (each word is 32 bits). If the host is performing

multiple reads or writes to consecutive memory addresses (autoincrement HPID cycles), the FIFOs are

used for bursting. The HPI DMA logic reads or writes a burst of four words at a time when accessing one

of the FIFOs.

Bursting is essentially invisible to the host because the host interface signaling is not affected. Its benefit

to the host is that the HRDY signal is deasserted less often when there are multiple reads or writes to

consecutive addresses.

Figure 28. FIFOs in the HPI

6.1

Read Bursting

When the host writes to the read address register (HPIAR), the read FIFO is flushed. Any host read data

that was in the read FIFO is discarded (the read FIFO pointers are reset). If an HPI DMA write to the read

FIFO is in progress at the time of a flush request, the HPI allows this write to complete and then performs

the flush.

After any read FIFO flush, no read cycles are being initiated. Read bursting can begin in one of two ways:

the host initiates an HPID read cycle with autoincrementing, or the host initiates issues a FETCH

command (writes 1 to the FETCH bit in HPIC).

32

Host Port Interface (HPI)

SPRUGK7A – March 2009 – Revised July 2010

Copyright © 2009–2010, Texas Instruments Incorporated