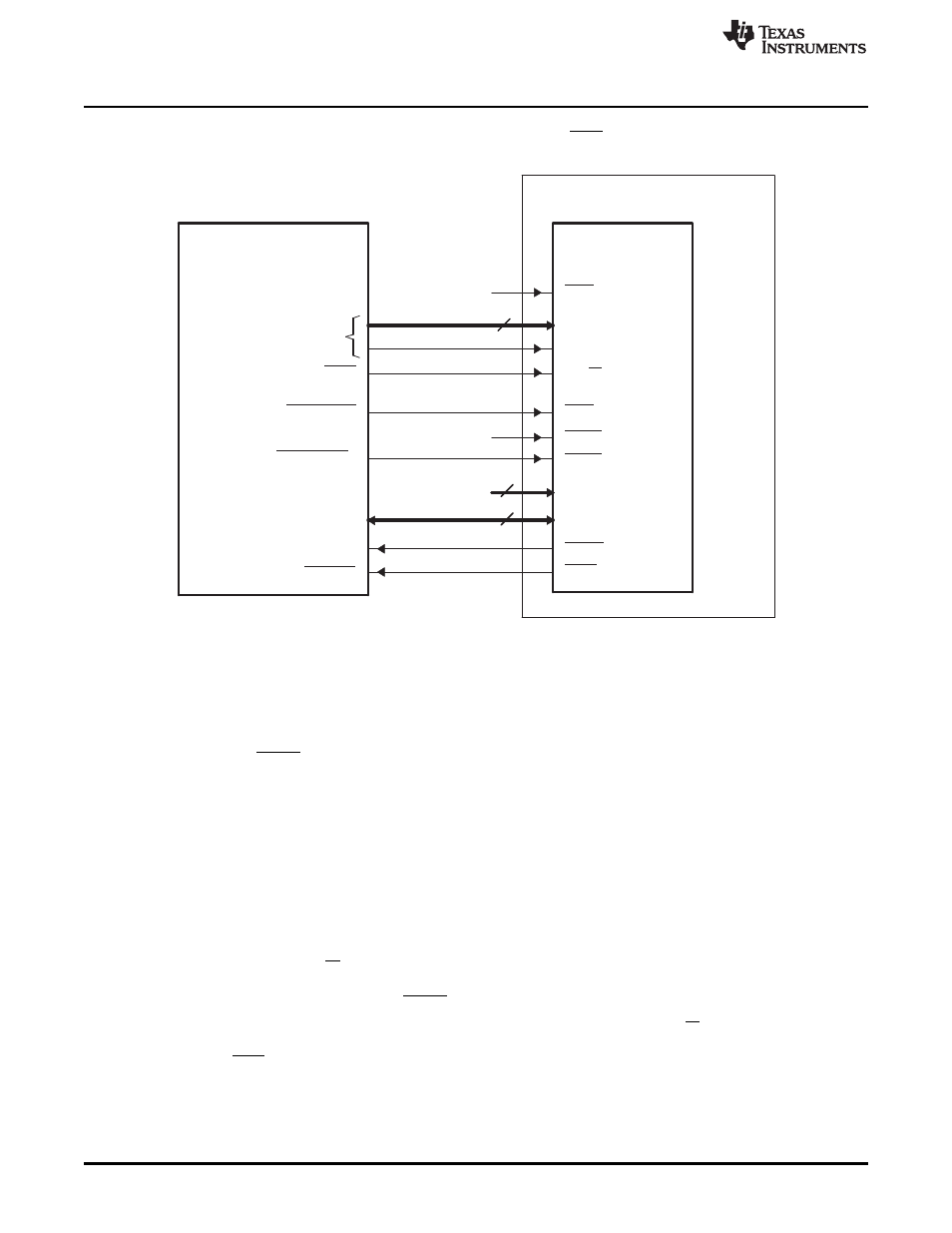

2 hpi configuration and data flow, Figure 5 – Texas Instruments TMS320C6457 User Manual

Page 14

Read/Write

Chip select

Data strobe

A

Data

Interrupt

Ready

HCNTL[1:0]

HR/W

HCS

HDS1

HDS2

HD[15:0]

HINT

HRDY

HPI

DSP

Host

HAS

HHWIL

Logic high

Logic high

Address

or I/O

HD[31:16]

No connect

2

16

16

HPI Operation

www.ti.com

Figure 5. Example of Host-DSP Signal Connections When the HAS Signal is Tied High in the 16-Bit

Multiplexed Mode

A

Data strobing options are given in

3.2

HPI Configuration and Data Flow

In multiplexed mode, the HPIC and HPIA must be initialized before valid host access cycles can take

place. The CPU and host must follow these steps to configure the HPI initially:

1. The CPU clears the HPIRST bit in the HPI register. All host accesses will be held off by the

deassertion of HRDY until HPIRST is cleared.

2. After the HPIRST bit is cleared, the host writes the HPIC register to program the halfword ordering bit

(HWOB) and the HPIA-related bits (DUALHPIA and HPIARWSEL). The HWOB bit must be

programmed before any accesses to the HPID and HPIA registers because this bit defines the

ordering of all halfword accesses in the 16-bit multiplexed mode.

3. The host writes the desired internal DSP word address to an address register (HPIAR and/or HPIAW).

introduces the two HPIA registers and their interaction with the host.

4. The host either reads from or writes to the data register (HPID). Data transfers between HPID and the

internal resources of the DSP are handled by the HPI DMA logic.

Each step of the access uses the same bus. Therefore, the host must drive the appropriate levels on the

HCNTL1 and HCNTL0 signals to indicate which register is to be accessed. The host must also drive the

appropriate level on the HR/W signal to indicate the data direction (read or write) and must drive other

control signals as appropriate. When HPI resources are temporarily busy or unavailable, the HPI informs

the host by deasserting the HPI-ready (HRDY) output signal.

When performing an access, the HPI first latches the levels on HCNTL[1:0], HR/W, and other control

signals. This latching can occur on the falling edge of the internal strobe signal (see

) or the

falling edge of HAS (see

). After the control information is latched, the HPI initiates an access

based on the control signals.

14

Host Port Interface (HPI)

SPRUGK7A – March 2009 – Revised July 2010

Copyright © 2009–2010, Texas Instruments Incorporated