Texas Instruments TMS320C6457 User Manual

Page 39

www.ti.com

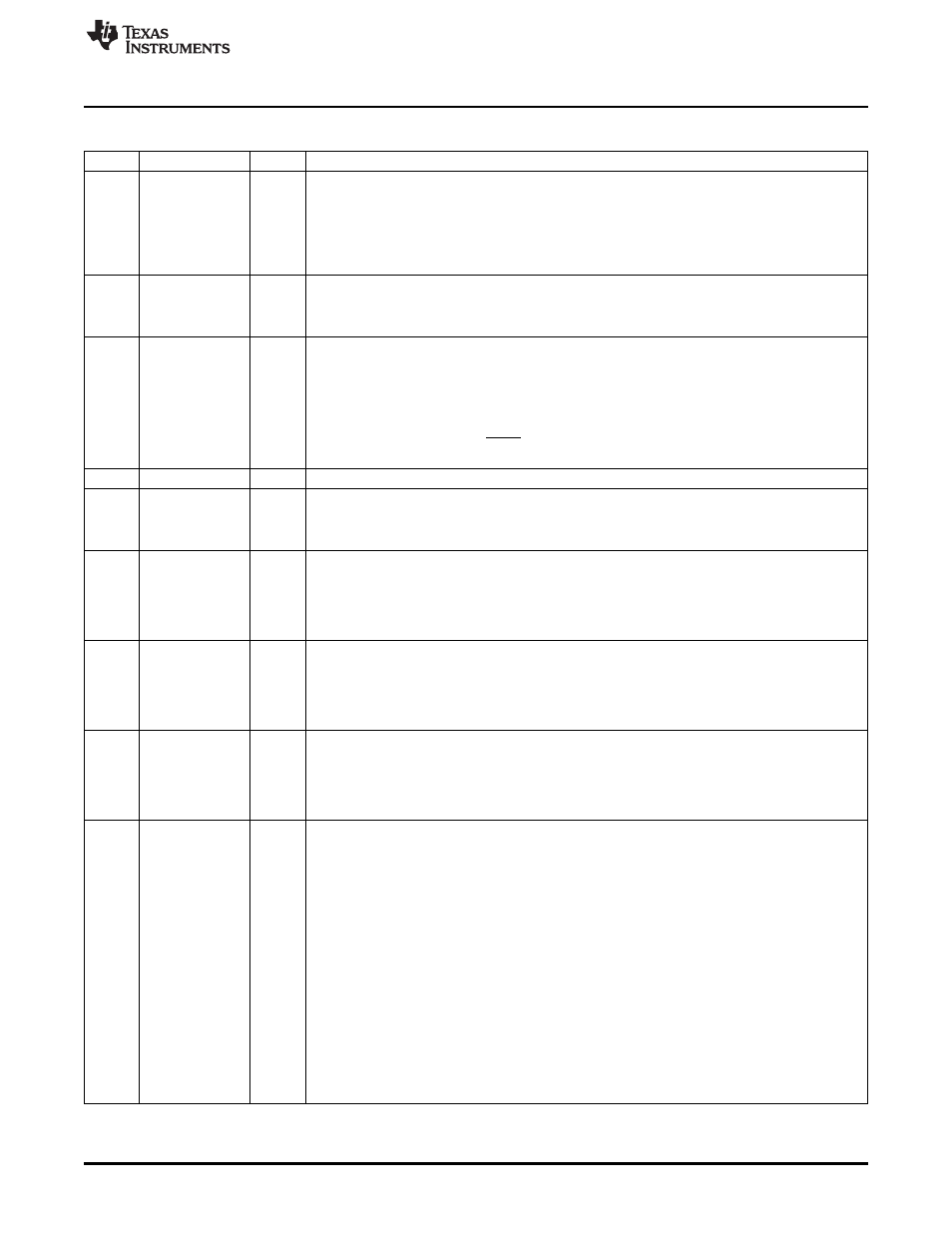

HPI Registers

Table 8. Host Port Interface Control Register (HPIC) Field Descriptions (continued)

Bit

Field

Value

Description

9

DUALHPIA

Dual-HPIA mode bit (configured by the host).

0

Single-HPIA mode. From the host's perspective, there is one 32-bit HPIA register. A host HPIA

write cycle places the same value in both HPIAR and HPIAW. During autoincrementing, both

HPIAR and HPIAW are incremented. A host HPIA read cycle retrieves the value from HPIAR.

1

Dual-HPIA mode. The host sees two 32-bit HPIA registers: HPIAR for read addresses and HPIAW

for write addresses.

8

HWOBSTAT

HWOB status bit. HWOBSTAT reflects the value of the HWOB bit (see bit 0).

0

HWOB bit = 0 (first halfword is most significant)

1

HWOB bit = 1 (first halfword is least significant)

7

HPIRST

HPI software reset bit (set by CPU).

0

Host: Reads of HPIRST always return 0.

CPU: Once the CPU has written 1 to HPIRST, reads return 0 until the FIFOs are completely reset.

Writing 0 before the reset process is complete will not stop the reset from occurring.

1

CPU: Writing 1 causes the read and write FIFOs and the associated FIFO logic to be reset. As

described in

, an active host cycle is allowed to complete before the reset process

begins. When HPIRST = 1, the HRDY pin is deasserted (not ready), thereby holding off all host

accesses. The CPU must set HPIRST = 0 to allow host accesses.

6-5

Reserved

0

The host must write 0s to these bits. The CPU cannot modify these bits.

4

FETCH

Host data fetch command bit (set by host).

0

CPU/Host: Reads of FETCH always return 0.

1

Host: Write 1 to tell the HPI DMA logic to pre-fetch data into the read FIFO.

3

HRDY

HPI-ready indicator (read-only).

0

Host: Internal HRDY is low. The HPI is not ready to complete a host cycle.

CPU: Reads of HRDY always return 0.

1

Host: Internal HRDY is high. The HPI is ready to complete a host cycle.

Note: HRDY bit is not the same as the HRDY pin status. Refer to Section 4 for details.

2

HINT

Host interrupt bit (set by the CPU, cleared by the host).

0

CPU/Host: Writing 0 has no effect.

1

CPU: Writing 1 to HINT generates a CPU-to-host interrupt. HINT remains 1 until it is cleared by the

host or by a hardware reset.

Host: Writing 1 to HINT clears HINT to 0, to acknowledge the CPU-to-host interrupt.

1

DSPINT

DSP interrupt bit (set by the host, cleared by the CPU).

0

CPU/Host: Writing 0 has no effect.

1

CPU: Writing 1 to DSPINT clears DSPINT to 0, to acknowledge the host-to-CPU interrupt.

Host: Writing 1 to DSPINT generates a host-to-CPU interrupt. DSPINT remains 1 until it is cleared

by the CPU or by a hardware reset.

0

HWOB

Halfword order bit (configured by the host). This bit is applicable only in the 16-bit multiplexed

mode. HWOB must be initialized by the host before the first data or address register access. The

status of HWOB is also reflected in HWOBSTAT (see bit 8).

For host write cycle:

0

The first halfword received from the bus is most significant (written to the high half of

HPID/HPIC/HPIAR/HPIAW). The second halfword is least significant (written to the low half of

HPID/HPIC/HPIAR/HPIAW).

1

The first halfword received from the bus is least significant (written to the low half of

HPID/HPIC/HPIAR/HPIAW). The second halfword is most significant (written to the high half of

HPID/HPIC/HPIAR/HPIAW).

For host read cycle:

0

The first halfword transmitted on the bus is most significant (taken from the high half of

HPID/HPIC/HPIAR/HPIAW). The second halfword is least significant (taken from the low half of

HPID/HPIC/HPIAR/HPIAW).

1

The first halfword transmitted on the bus is least significant (taken from the low half of

HPID/HPIC/HPIAR/HPIAW). The second halfword is most significant (taken from the high half of

HPID/HPIC/HPIAR/HPIAW).

39

SPRUGK7A – March 2009 – Revised July 2010

Host Port Interface (HPI)

Copyright © 2009–2010, Texas Instruments Incorporated