3 host port interface control register (hpic), Section 8.3 – Texas Instruments TMS320C6457 User Manual

Page 38

HPI Registers

www.ti.com

8.3

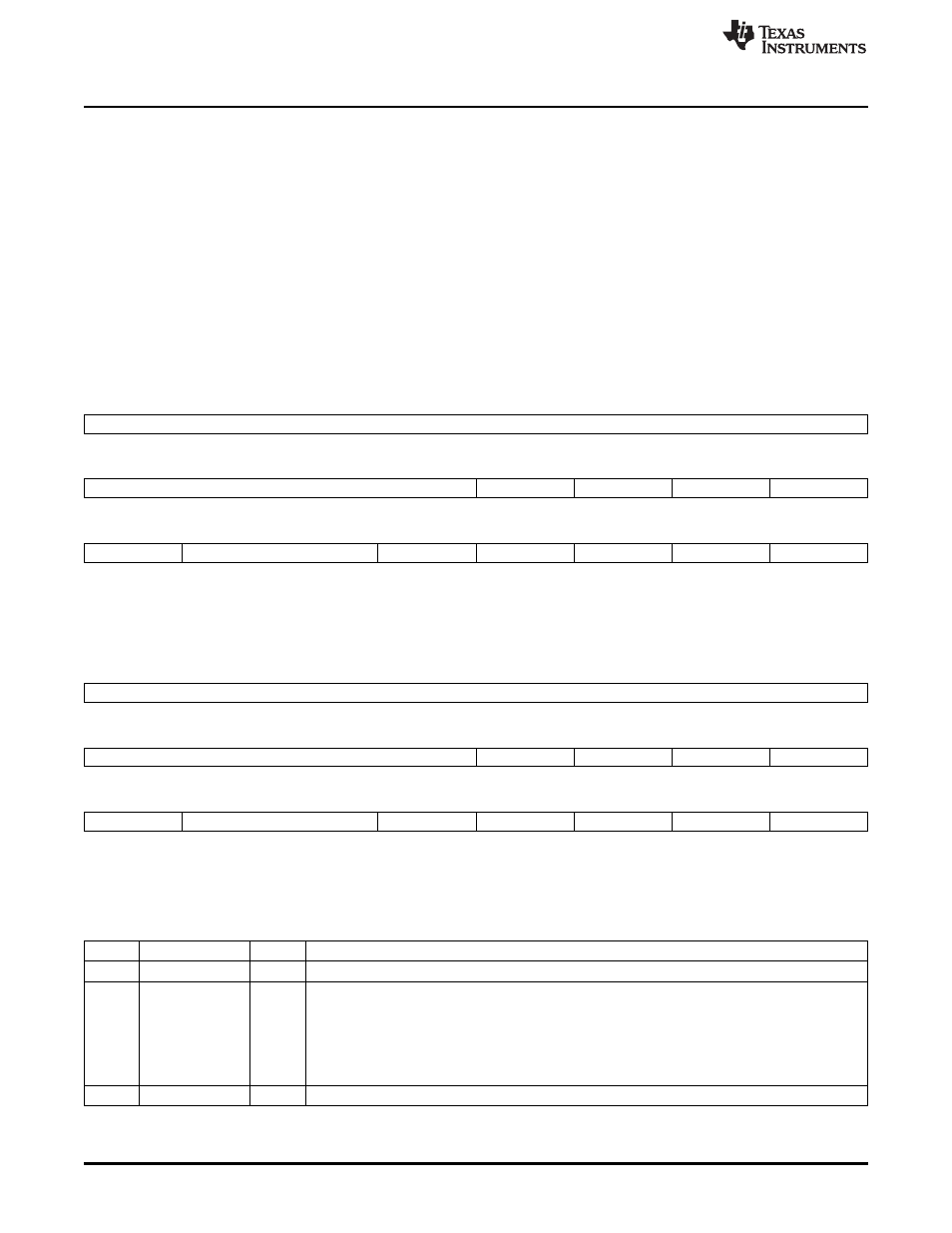

Host Port Interface Control Register (HPIC)

The HPIC register stores control and status bits used to configure and operate the HPI peripheral. The bit

positions of the HPIC register and their functions are illustrated in

.

In 16-bit multiplexed mode, the lower 16 bits of the HPIC register are duplicated on the upper 16 bits

during host accesses. Therefore, reading the upper or lower halfword of the HPIC register returns the

same value.

As shown in

and

, the host and the CPU do not have the same access permissions.

The host owns HPIC and thus has full read/write access. The CPU has primarily read-only access, but the

exceptions are:

•

The CPU can write 1 to the HINT bit to generate an interrupt to the host.

•

The CPU can write 1 to the DSPINT bit to clear/acknowledge an interrupt from the host.

The host port interface control register is shown in

and

and described in

.

Figure 30. Host Access Permissions

31

16

Reserved

R-0

15

12

11

10

9

8

Reserved

HPIARWSEL

Reserved

DUALHPIA

HWOBSTAT

R-0

R/W-0

R-0

R/W-0

R-0

7

6

5

4

3

2

1

0

HPIRST

Reserved

(A)

FETCH

HRDY

HINT

DSPINT

HWOB

R-0

R/W-0

R/W-0

R-1

R/W1C-0

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear (writing 0 has no effect); -n = value after reset

A.

Always keep this bit as zero.

Figure 31. CPU Access Permissions

31

16

Reserved

R-0

15

12

11

10

9

8

Reserved

HPIARWSEL

Reserved

DUALHPIA

HWOBSTAT

R-0

R-0

R-0

R-0

R-0

7

6

5

4

3

2

1

0

HPIRST

(A)

Reserved

FETCH

HRDY

HINT

DSPINT

HWOB

R/W-0 or 1

R-0

R-0

R-0

R/W-0

R/W-0

R-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

A.

This bit defaults to 0 when HPI boot is selected; otherwise it defaults to 1.

Table 8. Host Port Interface Control Register (HPIC) Field Descriptions

Bit

Field

Value

Description

31-12

Reserved

0

Read-only reserved bits. Reads return 0.

11

HPIARWSEL

HPIA read/write select bit (configured by the host). This bit is applicable only in the dual-HPIA mode

(DUALHPIA = 1).

Note: HPIARWSEL does not affect the HPI DMA logic. Regardless of the value of HPIARWSEL,

the HPI DMA logic uses HPIAW when writing to memory and HPIAR when reading from memory..

0

In the next HPIA host cycle, the host will access HPIAW (the write address register).

1

In the next HPIA host cycle, the host will access HPIAR (the read address register).

10

Reserved

0

Read-only reserved bits. Reads return 0.

38

Host Port Interface (HPI)

SPRUGK7A – March 2009 – Revised July 2010

Copyright © 2009–2010, Texas Instruments Incorporated