Section 8.2 – Texas Instruments TMS320C6457 User Manual

Page 37

www.ti.com

HPI Registers

8.2

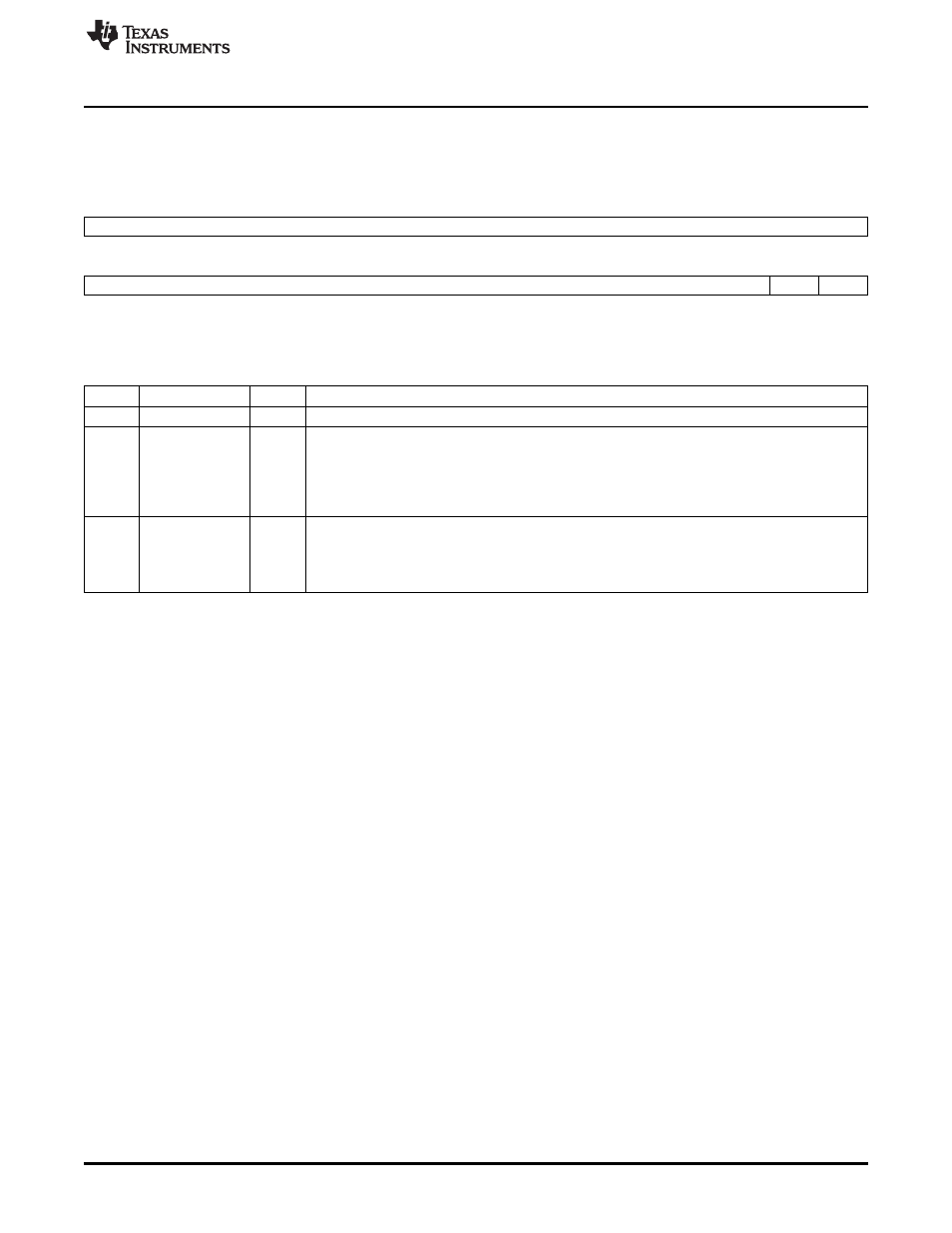

Power and Emulation Management Register (PWREMU_MGMT)

The power management and emulation register is shown in

and described in

Figure 29. Power and Emulation Management Register (PWREMU_MGMT)

31-16

Reserved

R-0

15-2

1

0

Reserved

SOFT

FREE

R-0

R/W-0

R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 7. Power and Emulation Management Register (PWREMU_MGMT) Field Descriptions

Bit

Field

Value

Description

31-2

Reserved

Reserved

1

SOFT

Determines emulation mode functionality of the HPI. When the FREE bit is cleared, the SOFT bit

selects the HPI mode.

0

Upon emulation suspend, the HPI operation is not affected.

1

In response to an emulation suspend event, the HPI logic halts after the current HPI transaction is

completed.

0

FREE

Free run emulation control. Determines emulation mode functionality of the HPI. When the FREE

bit is cleared, the SOFT bit selects the HPI mode.

0

The SOFT bit selects the HPI mode.

1

The HPI runs free regardless of the SOFT bit.

37

SPRUGK7A – March 2009 – Revised July 2010

Host Port Interface (HPI)

Copyright © 2009–2010, Texas Instruments Incorporated