Cpu 1 cpu 2 he-sl csb5, Ciob – Intel SERVER BOARD SDS2 User Manual

Page 85

Intel® Server Board SDS2

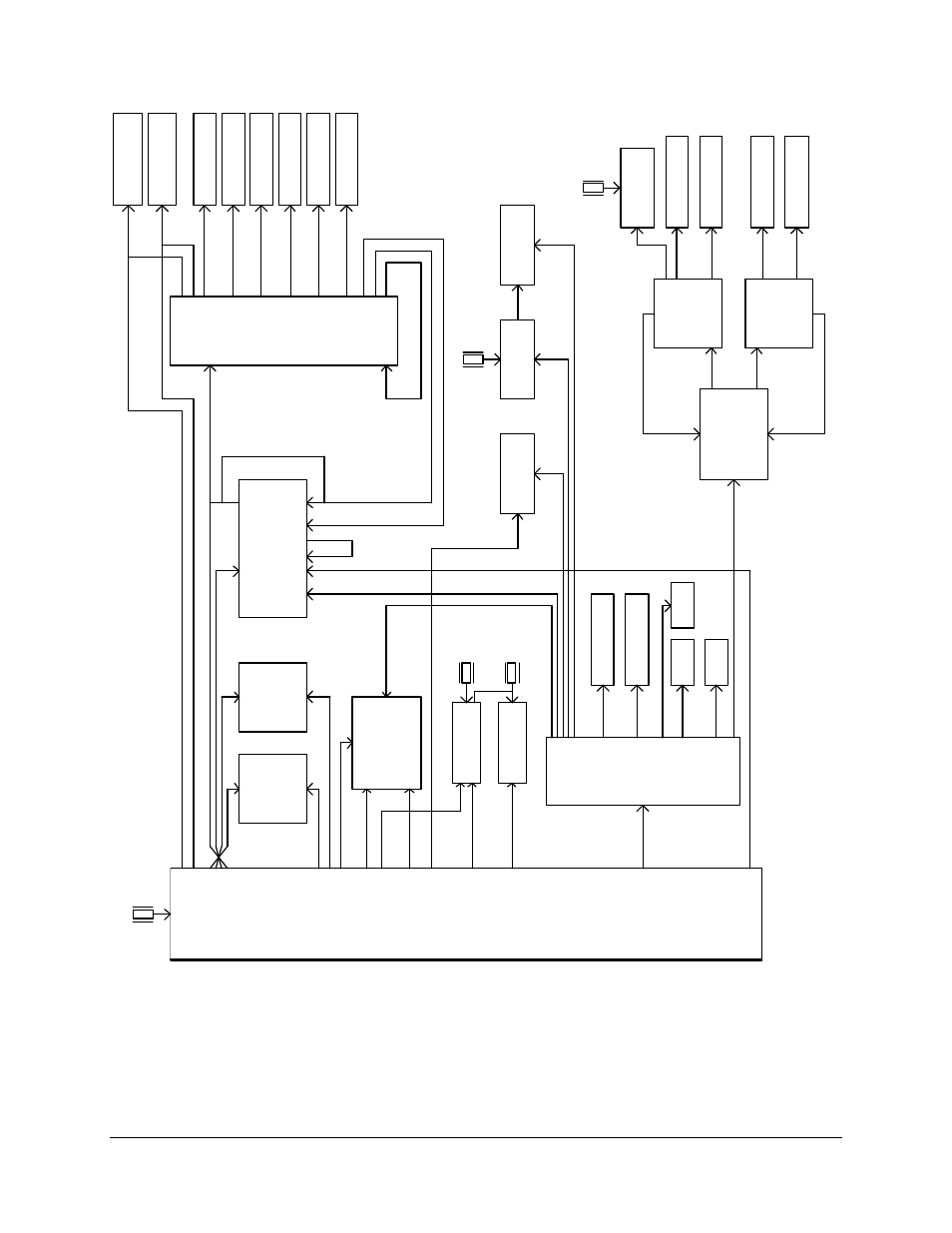

Clock/Voltage Generation and Distribution

Revision 1.2

Order Number: A85874-002

71

HOST CLK

APIC CLK

48 MHz

14 MHz

PCI 33MHz CLK

PCI 66MHz CLK

CPU 1

CPU 2

HE-SL

CSB5

PCI 33MHz

CLK

BUFFER

SDRAM

CLK PLL

VGA

SDRAM 1

SDRAM 2

SDRAM 3

SDRAM 4

SDRAM 5

SDRAM 6

SDRAM

REGISTER 1

CIOB

PCI

66MHz CLK

BUFFER

PCI SLOT 2

PCI SLOT 1

PCI SLOT 6

PCI SLOT 5

NIC 1

NIC 2

SIO

BMC

U160 SCSI

PCI SLOT 3

PCI SLOT 4

IRQ 0

IRQ 1

cPLD

SDRAM

REGISTER 2

133 MHz

133 MHz

133 MHz

PCI

66MHz CLK

BUFFER

16 MHz

16 MHz

16 MHz

48 MHz

48 MHz

14 MHz

14 MHz

33 MHz

33 MHz

33 MHz

66 MHz

66 MHz

66 MHz

66 MHz

66 MHz

66 MHz

66 MHz

66 MHz

66 MHz

66 MHz

25 MHz

AGPFBCLK

CNBDCLKIN

PLLCLKFB0

CNBDCLKFB

CNBRDCLK

133 MHz

133 MHz

133 MHz

133 MHz

133 MHz

133 MHz

133 MHz

133 MHz

133 MHz

133 MHz

133 MHz

40 MHz

32 KHz

40 MHz

25 MHz

14.318 MHz

33 MHz

33 MHz

33 MHz

33 MHz

33 MHz

33 MHz

33 MHz

Figure 8. SDS2 Server Board Clock Generation/Distribution Diagram

- 41210 (64 pages)

- 8xC251TQ (20 pages)

- ENTERPRISE PRINTING SYSTEM (EPS) 4127 (84 pages)

- U3-1L (20 pages)

- 80960HA (104 pages)

- X58 (54 pages)

- ESM-2850 2047285001R (91 pages)

- ATOM US15W (54 pages)

- D915GVWB (4 pages)

- XP-P5CM-GL (28 pages)

- AX965Q (81 pages)

- CORETM 2 DUO MOBILE 320028-001 (42 pages)

- CV700A (63 pages)

- 80C188EA (50 pages)

- X25-M (28 pages)

- XP-P5IM800GV (26 pages)

- IB868 (60 pages)

- D865GVHZ (88 pages)

- IB865 (64 pages)

- Altera P0424-ND (1 page)

- 8086-2 (30 pages)

- IXDP465 (22 pages)

- IWILL P4D (104 pages)

- GA-8I955X PRO (88 pages)

- FSB400 (PC2100) (96 pages)

- D845GLAD (4 pages)

- NAR-3041 (1 page)

- 87C196CA (136 pages)

- G52-M6734XD (74 pages)

- A96134-002 (10 pages)

- Express Routers 9000 (8 pages)

- 82540EP (45 pages)

- D865GLC (94 pages)

- IB850 (69 pages)

- MB898RF (62 pages)

- Arima LH500 (78 pages)

- V09 (33 pages)

- I/O Processor (22 pages)

- M600 (110 pages)

- SE7520JR2 (63 pages)

- SERVER BOARD S5520HCT (30 pages)

- Extensible Firmware Interface (1084 pages)

- GA-8IPXDR-E (70 pages)

- D845EBG2 (4 pages)

- AW8D (80 pages)