Intel SERVER BOARD SDS2 User Manual

Page 60

BIOS

Intel® Server Board SDS2

Revision 1.2

Order Number: A85874-002

46

The following table contains the POST codes displayed during the boot process. A beep code is

a series of individual beeps on the PC speaker, each of equal length. The following table

describes the error conditions associated with each beep code and the corresponding POST

checks point code as seen by a ‘port 80h’ card and LCD. For example, if an error occurs at

checkpoint 22h, a beep code of 1-3-1-1 is generated. The “-“ indicates a pause within the

sequence.

Some POST codes occur before the video display is initialized. To assist in determining the

fault, a unique beep-code is derived from these checkpoints as follows:

•

The 8-bit test point is broken down to four 2-bit groups.

•

Each group is made one-based (1 through 4)

•

One to four beeps are generated based on each group’s 2-bit pattern.

Note: Not all POST codes generate a Beep Code.

Example:

Checkpoint 4Bh is divided into:

01 00 10 11

The beep code is:

2 – 1 – 3 – 4

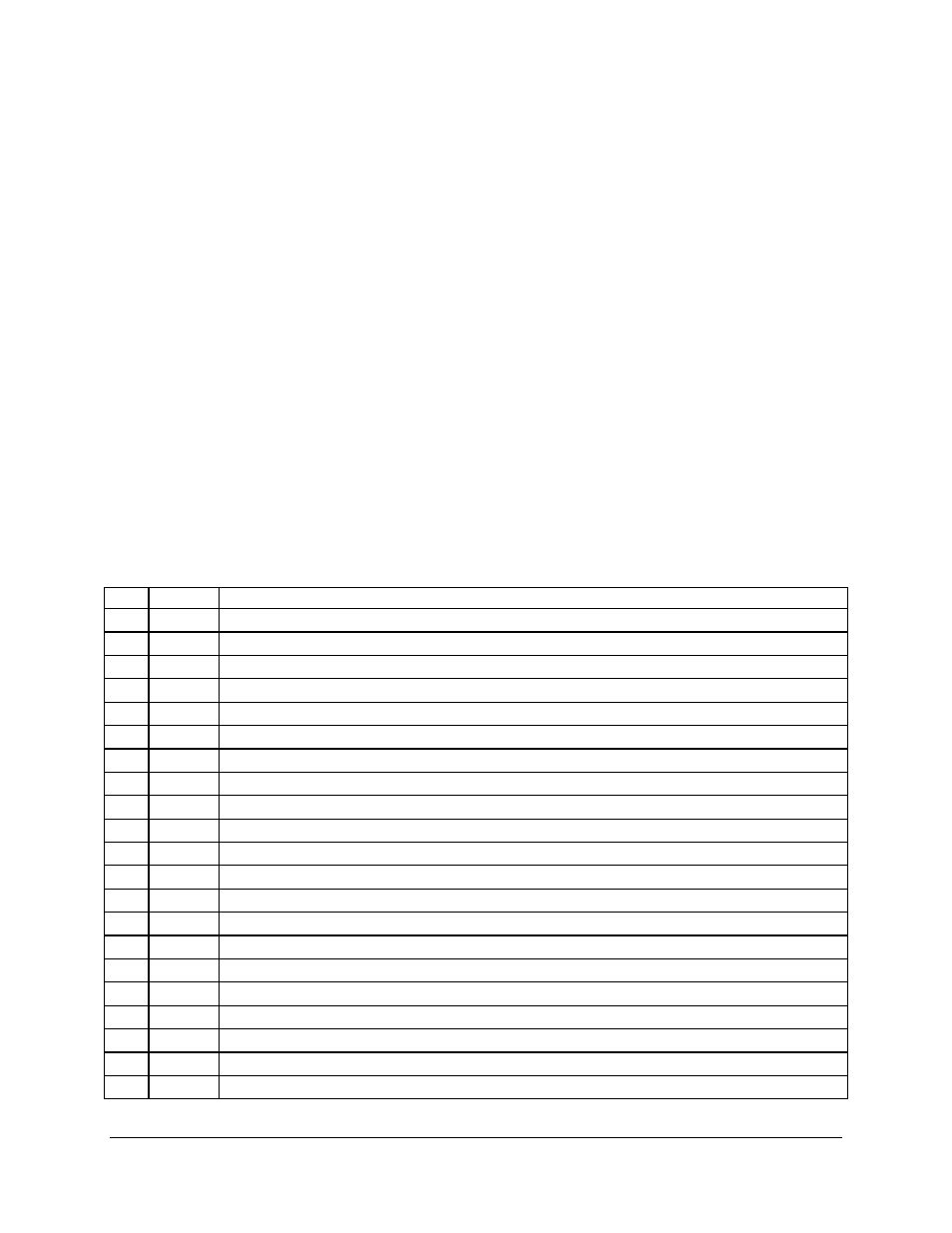

Table 27. Standard BIOS POST Codes

CP

Beeps

Reason

01

Initialize BMC

02

Verify Real Mode

03

Test BMC

04

Get Processor type

06

Initialize system hardware

08

Initialize chipset registers with initial POST values

09

Set in POST flag

0A

Initialize Processor registers

0B

Enable Processor cache

0C

Initialize caches to initial POST values

0E

Initialize I/O

0F

Initialize the local bus IDE

10

Initialize Power Management

11

Load alternate registers with initial POST values

12

Restore Processor control word during warm boot

13

Initialize PCI Bus mastering devices

14

Initialize keyboard controller

16

1-2-2-3

BIOS ROM checksum

17

Initialize external cache before memory auto size

18

8254 timer initialization

1A

8237 DMA controller initialization