Table d5. abbreviations for mnemonic encoding mat, And table d-5 – Intel 80C188XL User Manual

Page 395

INSTRUCTION SET OPCODES AND CLOCK CYCLES

D-22

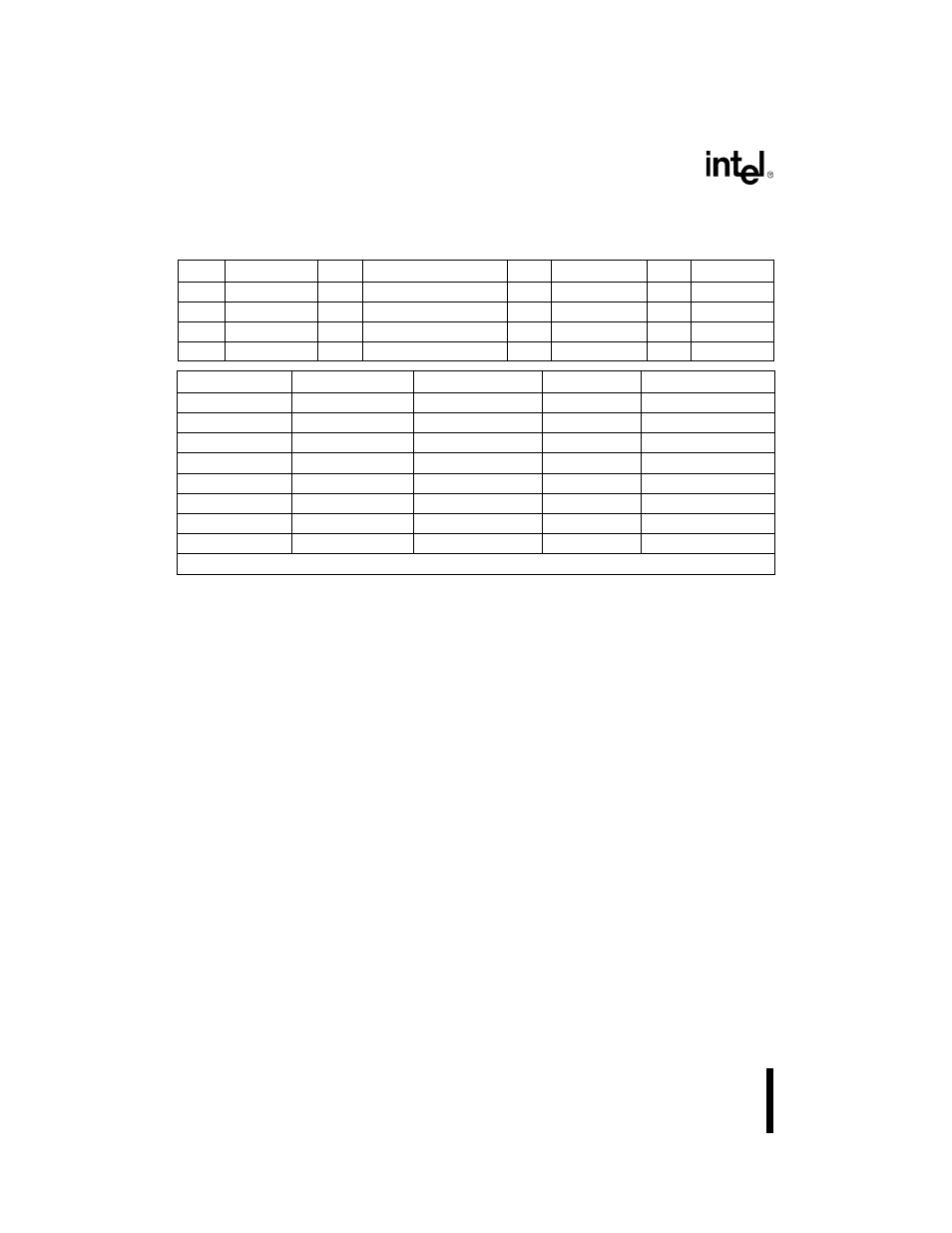

Table D-5. Abbreviations for Mnemonic Encoding Matrix

Abbr

Definition

Abbr

Definition

Abbr

Definition

Abbr

Definition

b

byte operation

ia

immediate to accumulator

m

memory

t

to CPU register

d

direct

id

indirect

r/m

EA is second byte

v

variable

f

from CPU register

is

immediate byte, sign extended

si

short intrasegment

w

word operation

i

immediate

l

long (intersegment)

sr

segment register

z

zero

Byte 2

Immed

Shift

Grp1

Grp2

mod 000 r/m

ADD

ROL

TEST

INC

mod 001 r/m

OR

ROR

—

DEC

mod 010 r/m

ADC

RCL

NOT

CALL id

mod 011 r/m

SBB

RCR

NEG

CALL l, id

mod 100 r/m

AND

SHL/SAL

MUL

JMP id

mod 101 r/m

SUB

SHR

IMUL

JMP i, id

mod 110 r/m

XOR

—

DIV

PUSH

mod 111 r/m

CMP

SAR

IDIV

—

mod and r/m determine the Effective Address (EA) calculation. See Table D-1 for definitions.

This manual is related to the following products: