Figure 610. mcs3:0 active ranges, Table 65. mcs block size and start address restri, Figure 6-10). the base addr – Intel 80C188XL User Manual

Page 169: Table 6-5 lis

CHIP-SELECT UNIT

6-14

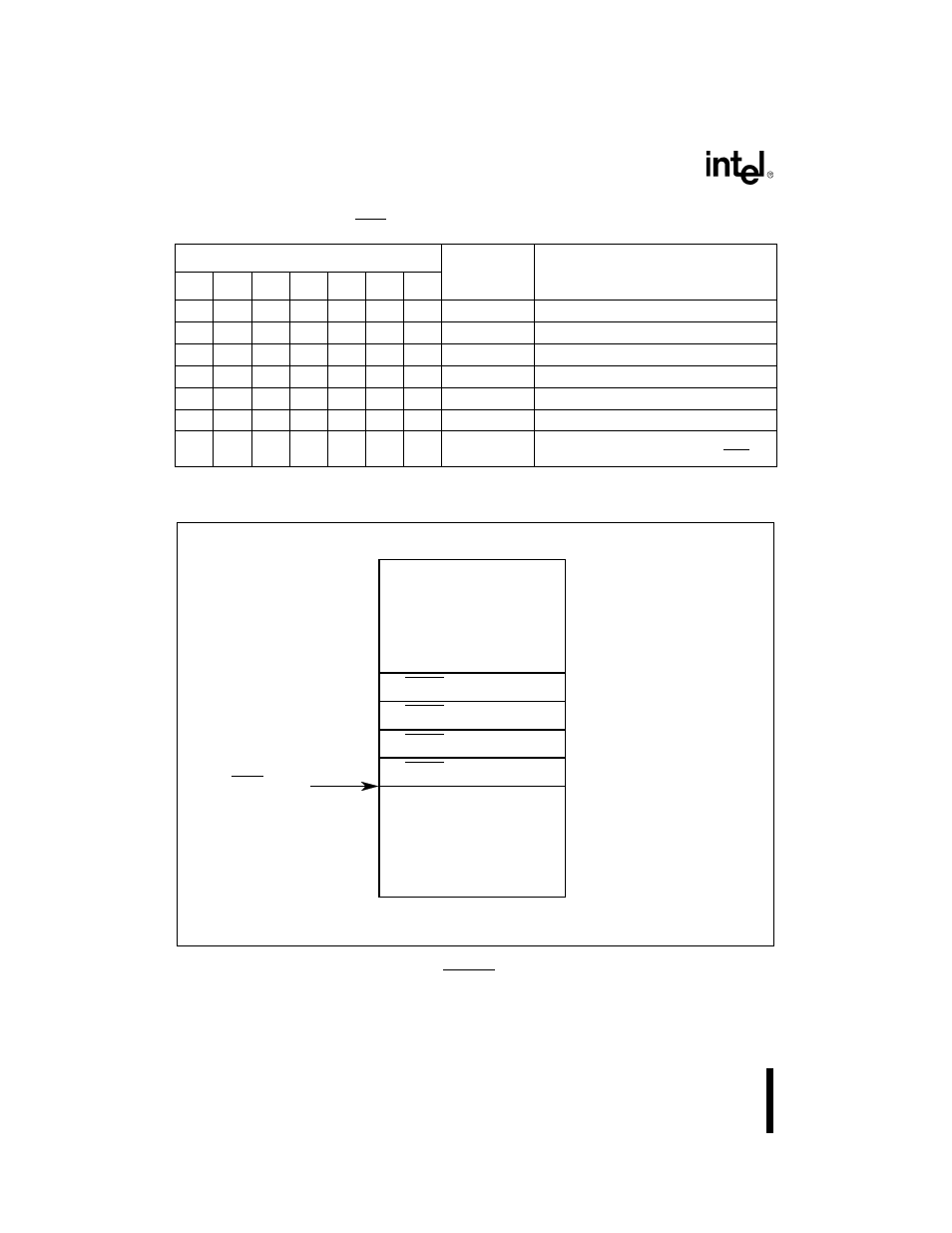

Figure 6-10. MCS3:0 Active Ranges

Table 6-5. MCS Block Size and Start Address Restrictions

MPCS Block Size Bits

Block Size

(Kbytes)

MMCS Start Address

Restrictions

M6

M5

M4

M3

M2

M1

M0

0

0

0

0

0

0

1

8

None

0

0

0

0

0

1

X

16

U13 must be zero.

0

0

0

0

1

X

X

32

U14:13 must be zero.

0

0

0

1

X

X

X

64

U15:13 must be zero.

0

0

1

X

X

X

X

128

U16:13 must be zero.

0

1

X

X

X

X

X

256

U17:13 must be zero.

1

X

X

X

X

X

X

512

U18:13 must be zero.

NOTE: If U19 is one, will overlap UCS.

X= don’t care, but should be 0 for future compatibility.

MCS3 Active Range

MCS2 Active Range

MCS1 Active Range

MCS0 Active Range

Base + (Block Size-1)

Base + (3/4 Block Size-1)

Base + (1/2 Block Size-1)

Base + (1/4 Block Size-1)

Base + 3/4 Block Size

Base + 1/2 Block Size

Base + 1/4 Block Size

Memory Map

MCS Base

(Defined by U19:13)

Block Size is

defined by M6:0

Starting Address

Ending Address

A1136-0C