Intel 80C188XL User Manual

Page 369

INSTRUCTION SET DESCRIPTIONS

C-46

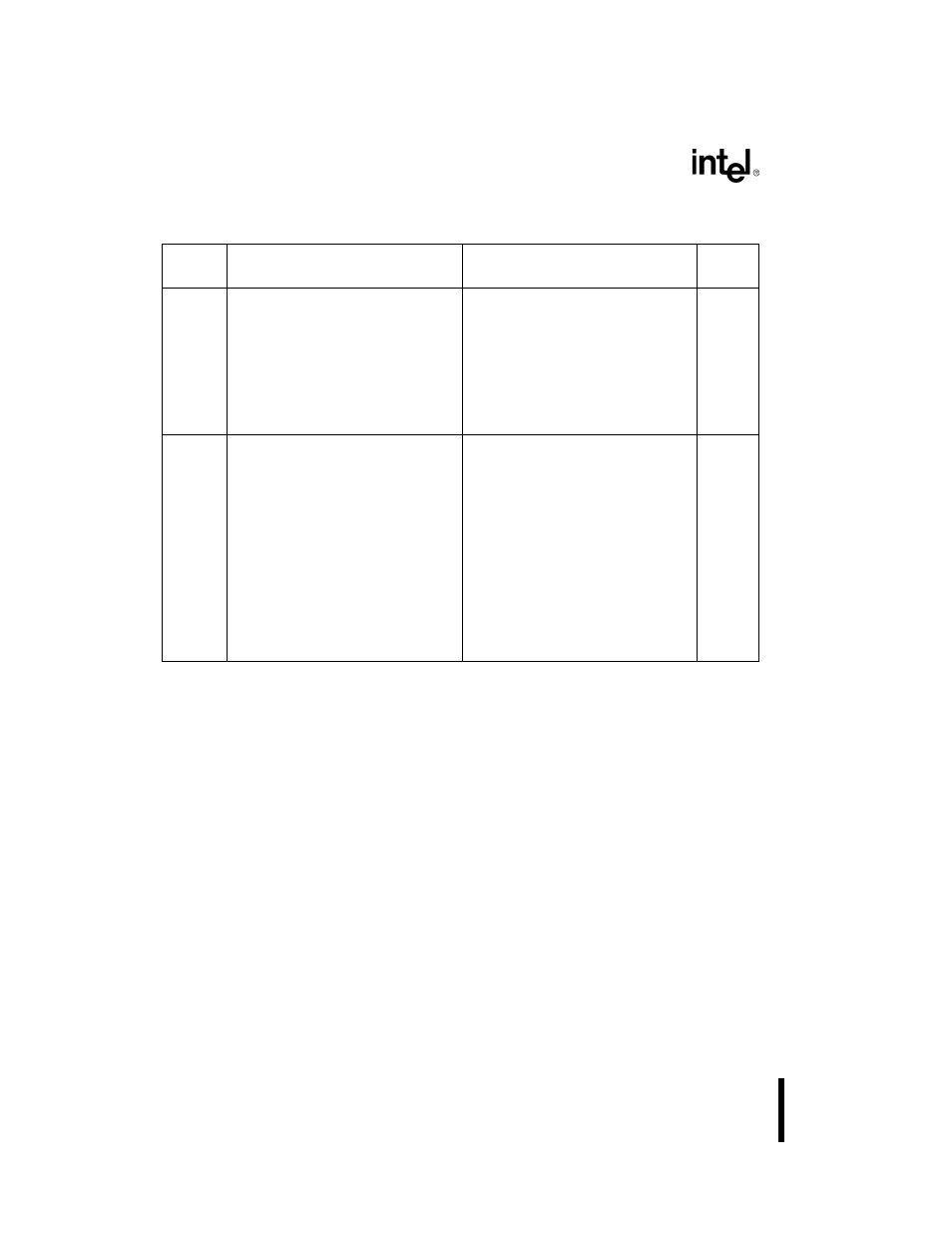

WAIT

Wait:

WAIT

Causes the CPU to enter the wait state

while its test line is not active.

Instruction Operands:

none

None

AF –

CF –

DF –

IF –

OF –

PF –

SF –

TF –

ZF –

XCHG

Exchange:

XCHG dest, src

Switches the contents of the source

and destination operands (bytes or

words). When used in conjunction with

the LOCK prefix, XCHG can test and

set a semaphore that controls access

to a resource shared by multiple

processors.

Instruction Operands:

XCHG accum, reg

XCHG mem, reg

XCHG reg, reg

(temp)

←

(dest)

(dest)

←

(src)

(src)

←

(temp)

AF –

CF –

DF –

IF –

OF –

PF –

SF –

TF –

ZF –

Table C-4. Instruction Set (Continued)

Name

Description

Operation

Flags

Affected

NOTE:

The three symbols used in the Flags Affected column are defined as follows:

– the contents of the flag remain unchanged after the instruction is executed

? the contents of the flag is undefined after the instruction is executed

ü

the flag is updated after the instruction is executed