5 in-service register, Figure 89. priority mask register – Intel 80C188XL User Manual

Page 213

INTERRUPT CONTROL UNIT

8-18

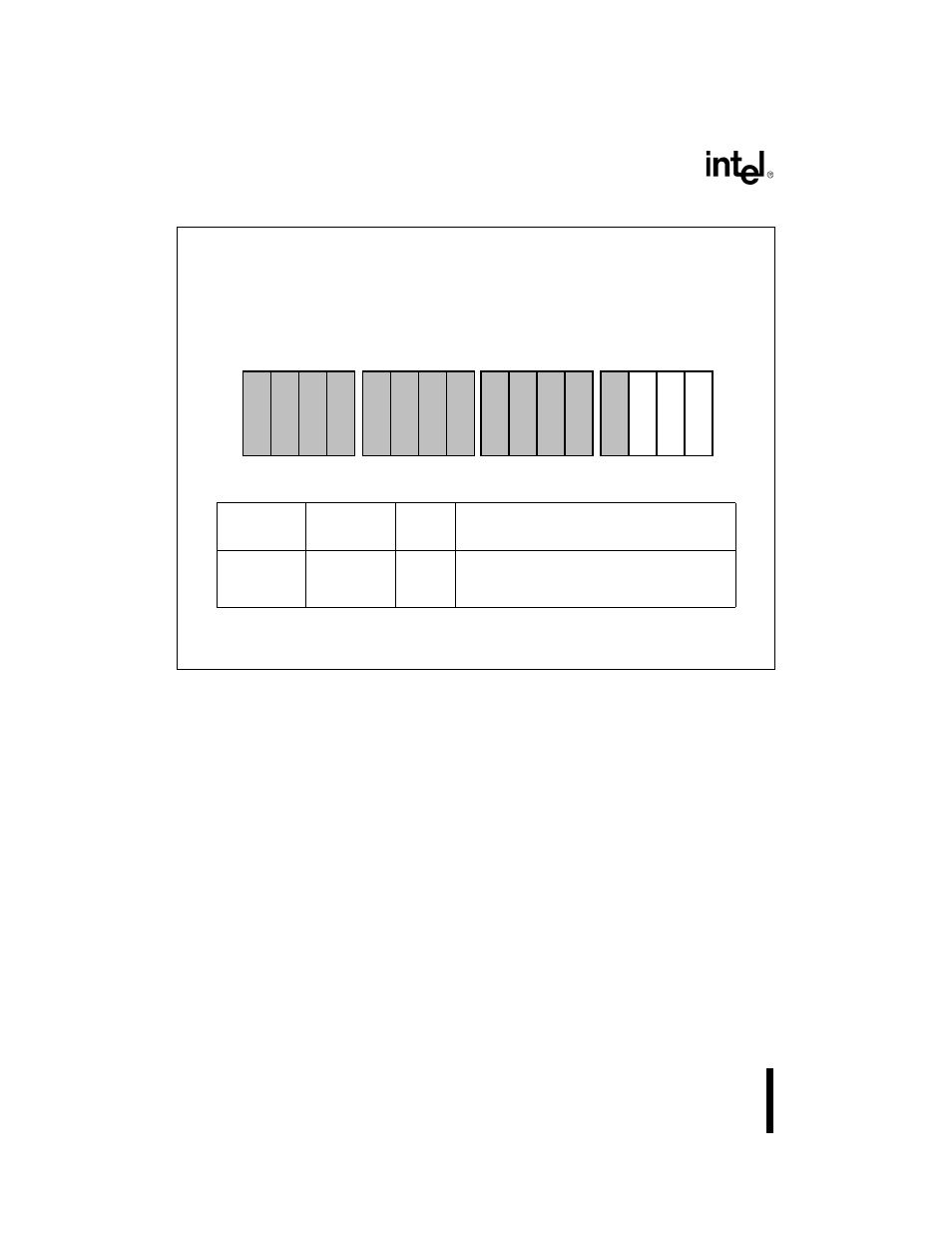

Figure 8-9. Priority Mask Register

8.4.5

In-Service Register

The In-Service register has a bit for each interrupt source. The bits indicate which source’s inter-

rupt handlers are currently executing. The In-Service bit is set when an interrupt is acknowl-

edged; the interrupt handler must clear it with an End-of-Interrupt (EOI) command. The Interrupt

Control Unit uses the In-Service register to support interrupt nesting.

Register Name:

Priority Mask Register

Register Mnemonic:

PRIMSK

Register Function:

Masks lower-priority interrupt sources

Bit

Mnemonic

Bit Name

Reset

State

Function

PM2:0

Priority

Mask

111

Defines a priority-based interrupt mask.

Interrupts whose priority is lower than this value

are masked.

NOTE:

Reserved register bits are shown with gray shading. Reserved bits must be written

to a logic zero to ensure compatibility with future Intel products.

A1216-A0

15

0

P

M

0

P

M

1

P

M

2