Table 210. interpretation of conditional transfer – Intel 80C188XL User Manual

Page 55

OVERVIEW OF THE 80C186 FAMILY ARCHITECTURE

2-26

Iteration control instructions can be used to regulate the repetition of software loops. These in-

structions use the CX register as a counter. Like the conditional transfers, the iteration control in-

structions are self-relative and can transfer only to targets that are within –128 to +127 bytes of

themselves. They are SHORT transfers.

The interrupt instructions allow programs and external hardware devices to activate interrupt ser-

vice routines. The effect of a software interrupt is similar to that of a hardware-initiated interrupt.

The processor cannot execute an interrupt acknowledge bus cycle if the interrupt originates in

software or with an NMI (Non-Maskable Interrupt).

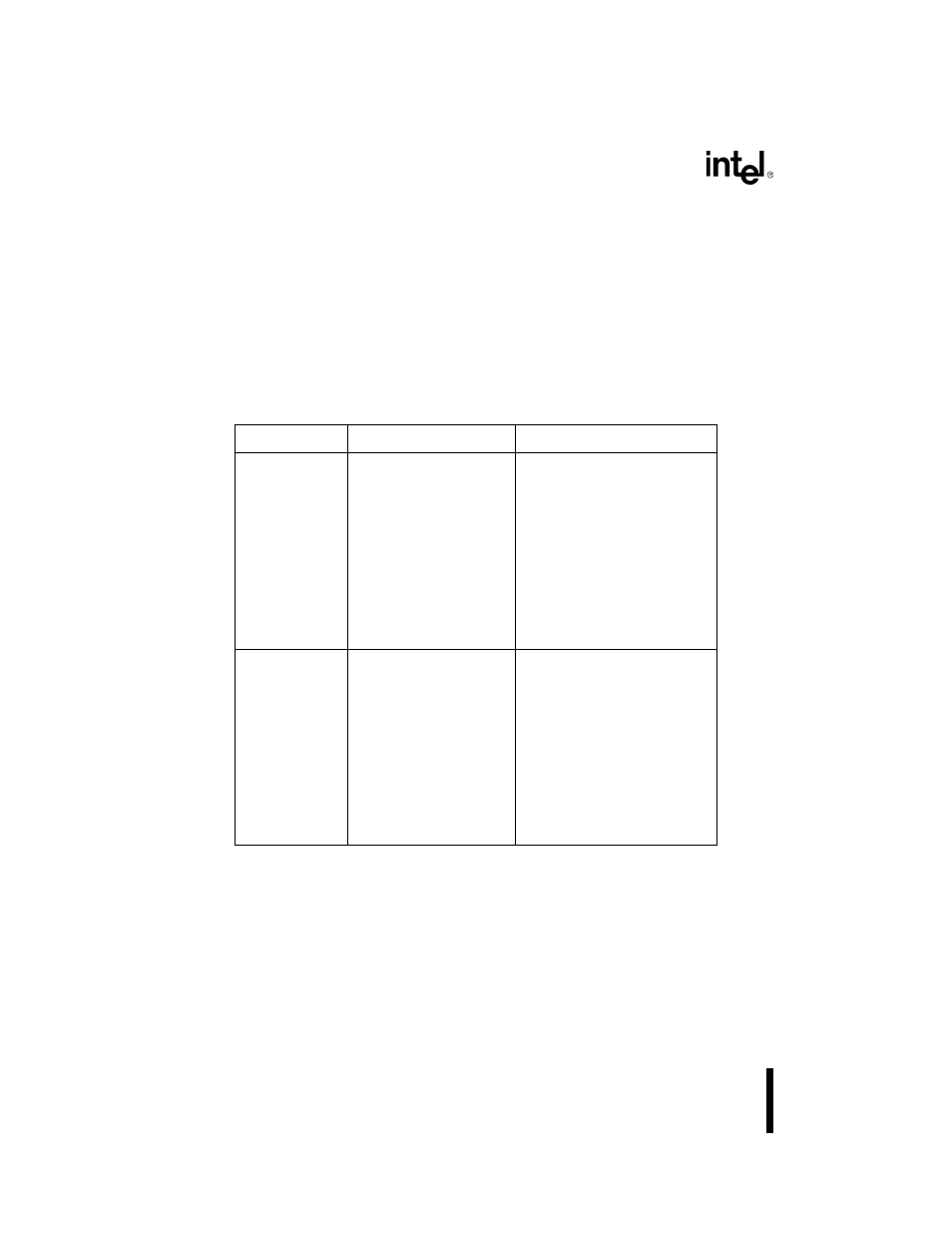

Table 2-10. Interpretation of Conditional Transfers

Mnemonic

Condition Tested

“Jump if…”

JA/JNBE

(CF or ZF)=0

above/not below nor equal

JAE/JNB

CF=0

above or equal/not below

JB/JNAE

CF=1

below/not above nor equal

JBE/JNA

(CF or ZF)=1

below or equal/not above

JC

CF=1

carry

JE/JZ

ZF=1

equal/zero

JG/JNLE

((SF xor OF) or ZF)=0

greater/not less nor equal

JGE/JNL

(SF xor OF)=0

greater or equal/not less

JL/JNGE

(SF xor OF)=1

less/not greater nor equal

JLE/JNG

((SF xor OF) or ZF)=1

less or equal/not greater

JNC

CF=0

not carry

JNE/JNZ

ZF=0

not equal/not zero

JNO

OF=0

not overflow

JNP/JPO

PF=0

not parity/parity odd

JNS

SF=0

not sign

JO

OF=1

overflow

JP/JPE

PF=1

parity/parity equal

JS

SF=1

sign

NOTE:

The terms above and below refer to the relationship of two unsigned values;

greater and less refer to the relationship of two signed values.