Figure 1011. dma control register – Intel 80C188XL User Manual

Page 270

10-15

DIRECT MEMORY ACCESS UNIT

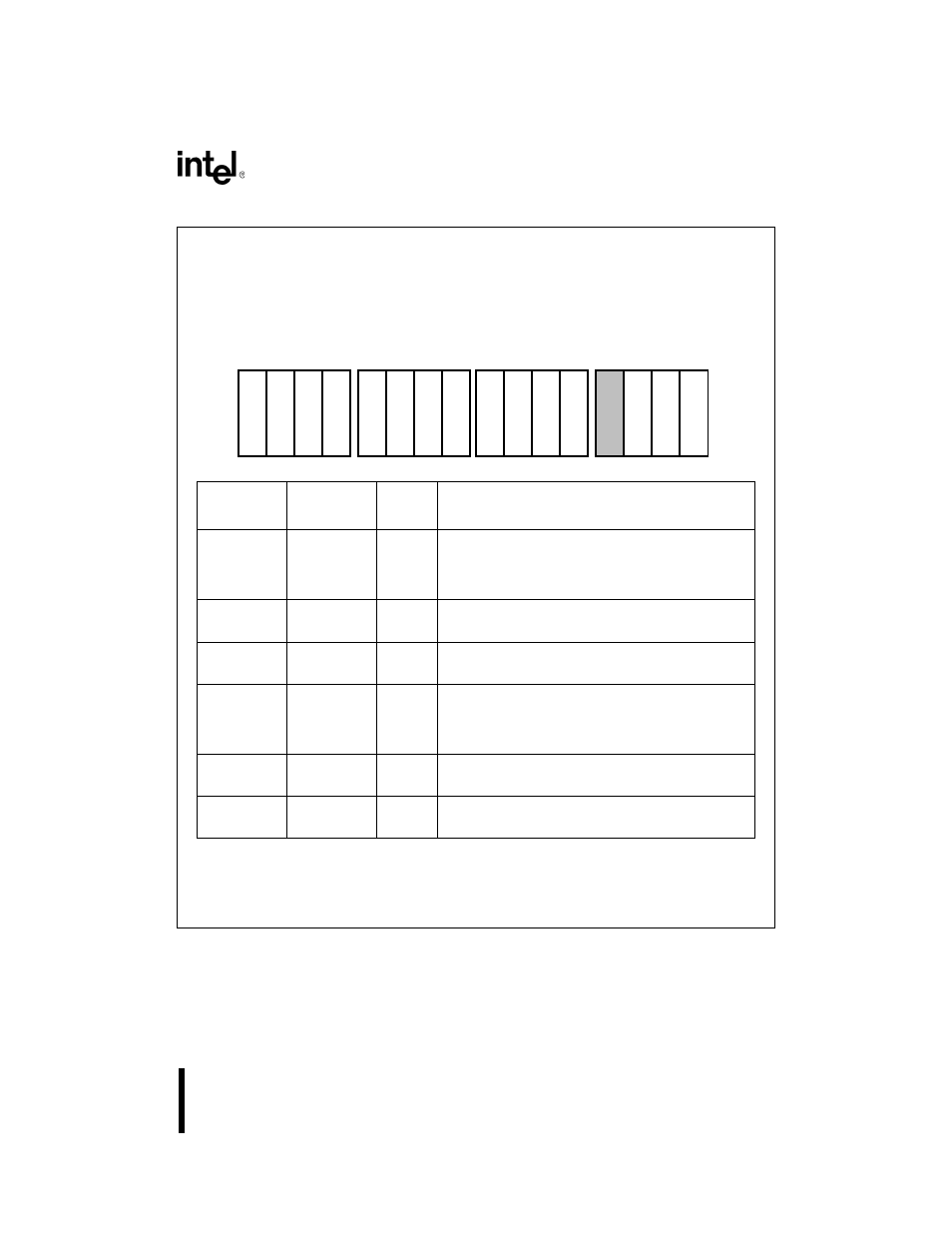

Figure 10-11. DMA Control Register

Register Name:

DMA Control Register

Register Mnemonic:

DxCON

Register Function:

Controls DMA channel parameters.

Bit

Mnemonic

Bit Name

Reset

State

Function

DMEM

Destination

Address

Space

Select

X

Selects memory or I/O space for the destination

pointer. Set DMEM to select memory space; clear

DMEM to select I/O space.

DDEC

Destination

Decrement

X

Set DDEC to automatically decrement the destination

pointer after each transfer. (See Note.)

DINC

Destination

Increment

X

Set DINC to automatically increment the destination

pointer after each transfer. (See Note.)

SMEM

Source

Address

Space

Select

X

Selects memory or I/O space for the source pointer.

Set SMEM to select memory space; clear SMEM to

select I/O space.

SDEC

Source

Decrement

X

Set SDEC to automatically decrement the source

pointer after each transfer. (See Note.)

SINC

Source

Increment

X

Set SINC to automatically increment the source

pointer after each transfer. (See Note.)

NOTE:

Reserved register bits are shown with gray shading. Reserved bits must be written to a

logic zero to ensure compatibility with future Intel products. A pointer remains constant if

its increment and decrement bits are equal.

15

0

S

T

R

T

C

H

G

W

O

R

D

P

S

Y

N

0

S

Y

N

1

I

D

R

Q

T

C

S

I

N

C

S

D

E

C

I

N

T

D

I

N

C

D

D

E

C

D

M

E

M

S

M

E

M

A1180-0A