Figure 318. normally ready system timings – Intel 80C188XL User Manual

Page 100

3-19

BUS INTERFACE UNIT

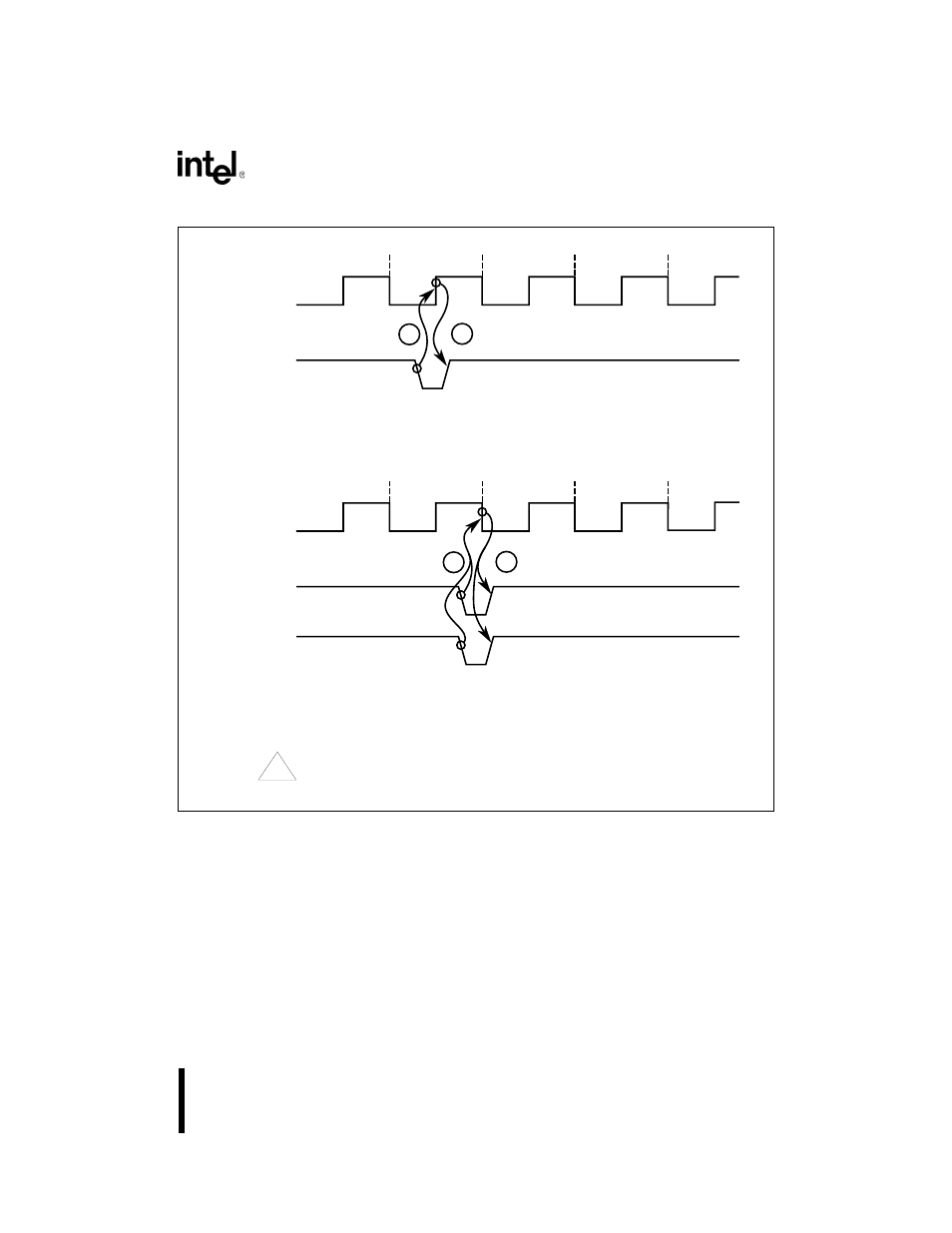

Figure 3-18. Normally Ready System Timings

Conditions causing the BIU to become idle include the following.

•

The instruction prefetch queue is full.

•

An effective address calculation is in progress.

•

The bus cycle inherently requires idle states (e.g., interrupt acknowledge, locked opera-

tions).

•

Instruction execution forces idle states (e.g., HLT, WAIT).

ARDY

CLKOUT

In a Normally-Ready system, a wait state will be inserted when 1 & 2 are met.

(Assumes SRDY is low.)

T2

T3

TW

ARDY

CLKOUT

Alternatively, in a Normally-Ready system, a wait state will be inserted

when1 & 2 are met for SRDY and ARDY.

1. TARYCL, TSRYCL : ARDY and SRDY low to clock low

2. TCHARX, TCLSRY : ARDY and SRDY low from clock low

T2

T3

TW

1

2

1

2

!

Failure to meet ARDY and SRDY setup and hold can cause a device failure

(i.e., the bus hangs or operates inappropriately).

1. TARYCH : ARDY low to clock high

2. TARYCHL : Clock high to ARDY high (ARDY inactive hold time)

SRDY

T4

T4

A1512-0A