2 ultra dma data burst timing requirements – FUJITSU MHR2030AT User Manual

Page 204

Interface

5-130

C141-E145-02EN

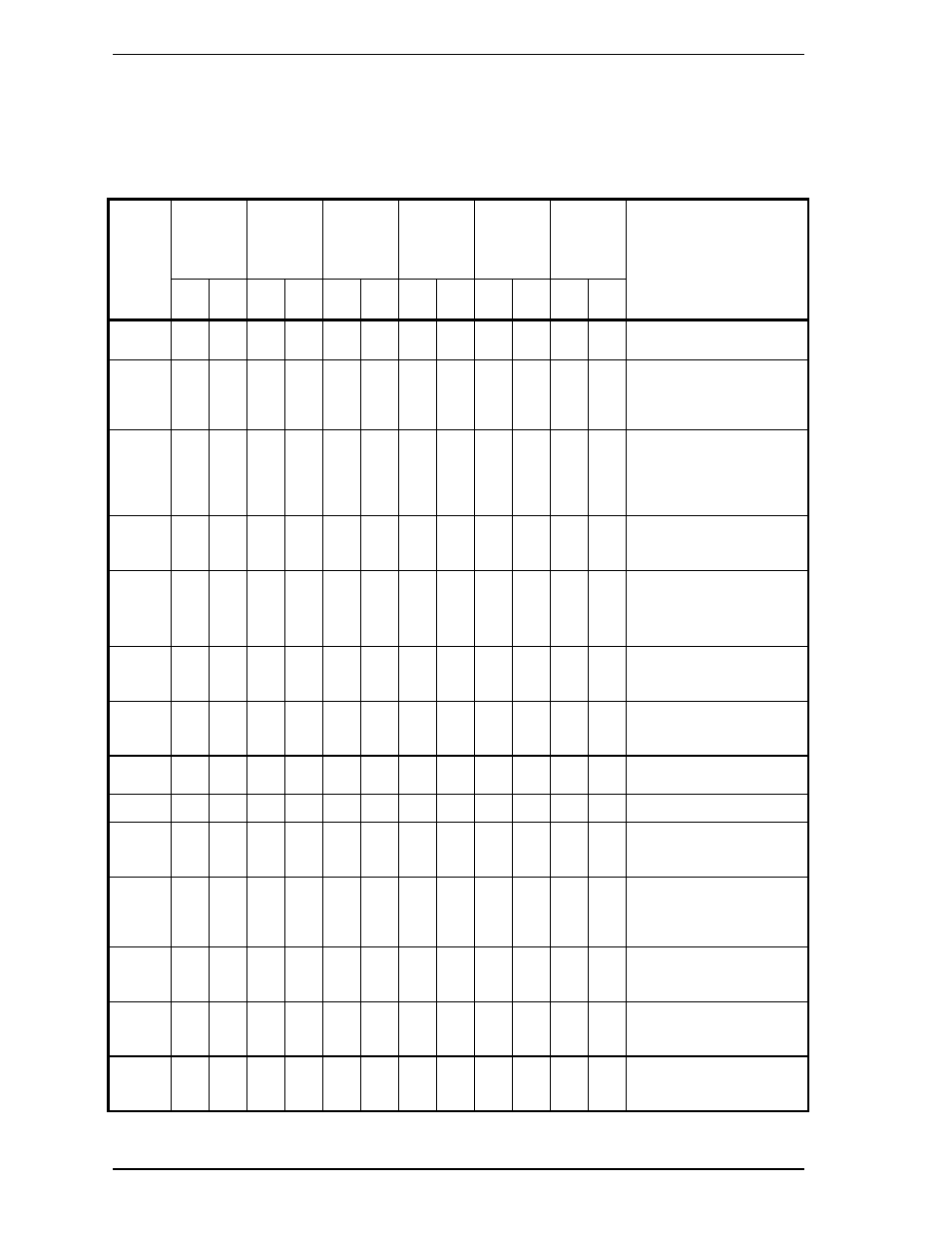

5.6.3.2 Ultra DMA data burst timing requirements

Table 5.18 Ultra DMA data burst timing requirements (1 of 2)

NAME MODE 0

(in ns)

MODE 1

(in ns)

MODE 2

(in ns)

MODE 3

(in ns)

MODE 4

(in ns)

MODE 5

(in ns)

COMMENT

MIN MAX MIN MAX MIN MAX

MIN MAX MIN

MAX MIN MAX

t

2CYCTYP

240

160

120

90

60

40

Typical sustained average two

cycle time

t

CYC

112

73

54

39

25

16.8

Cycle time allowing for

asymmetry and clock variations

(from STROBE edge to STROBE

edge)

t

2CYC

230

153

115

86

57

38

Two cycle time allowing for

clock variations (from rising edge

to next rising edge or from falling

edge to next falling edge of

STROBE)

t

DS

15

10

7

7

5

4

Data setup time at recipient (from

data valid until STROBE edge)

(*2), (*5)

t

DH

5

5

5

5

5

4.6

Data hold time at recipient (from

STROBE edge until data may

become invalid) (*2), (*5)

t

DVS

70

48

31

20

6.7

4.8

Data valid setup time at sender

(from data valid until STROBE

edge) (*3)

t

DVH

6.2

6.2

6.2

6.2

6.2

4.8

Data valid hold time at sender

(from STROBE edge until data

may become invalid) (*3)

t

CS

15

10

7

7

5

5

CRC word setup time at device

(*2)

t

CH

5

5

5

5

5

5

CRC word hold time device (*2)

t

CVS

70

48

31

20

6.7

10

CRC word valid setup time at

host (from CRC valid until

DMACK-negation) (*3)

t

CVH

6.2

6.2

6.2

6.2

6.2

10

CRC word valid hold time at

sender (from DMACK-negation

until CRC may become invalid)

(*3)

t

ZFS

0

0

0

0

0

35

Time from STROBE output

released-to-driving until the first

transition of critical timing

t

DZFS

70

48

31

20

6.7

25

Time from data output released-

to-driving until the first transition

of critical timing

t

FS

230

200

170

130

120

90

First STROBE time (for device to

first negate DSTROBE from

STOP during a data in burst)