Measurement Computing CIO-PDMAxx User Manual

Page 23

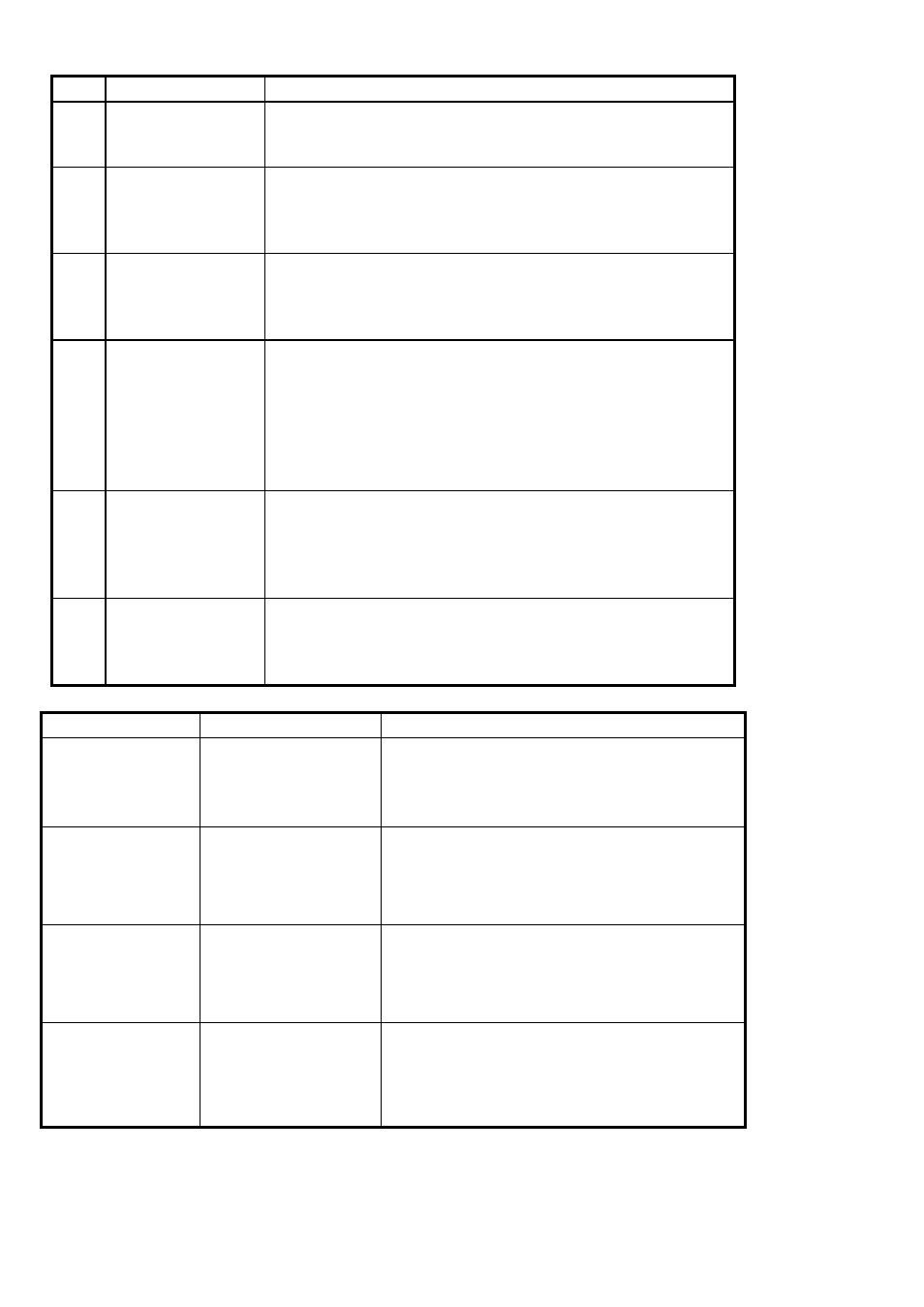

When this bit is set, the OVERRUN and UNDERRUN error

flags are enabled. The error flags should be enabled when a

REP transfer size of greater than one FIFO in depth is

required (512 bytes).

ERR_ENB

2

When this bit is set, port A and B outputs are double-

buffered so that the outputs are updated in sync with the

pacer clock. When this bit is cleared, port A and B outputs

are updated immediately following the write to the

corresponding port registers.

DBL_BUFF

3

When this bit is cleared, the sample counter (8254 Counter

2) is used to count the total number of samples to be

transferred (the sample counter decrements at the pacer

sample rate). When this bit is set and in REP-STRING mode,

the sample counter is used to count the total number of half-

full FIFO transfers to be transferred (the sample counter

decrements at the half-full rate)

HALF_FF_CNT

4

When this bit is set, the REP-STRING sequence operates in

continuous mode. In this mode the ARM register is enabled

and is used to trigger the termination of the current REP

transfer.

REP_CONT

5

When this bit is set REP-STRING sequence is initiated. This

bit is automatically cleared when the current REP-STRING

transfer has completed (the sample counter reaches terminal

count).

REP_ENB

6

When this bit is set REP mode is enabled. When this bit is

cleared REP mode is disabled and interrupt status

corresponding to the REP function is also inactive.

REP_MODE

7

Description

Name

Bit

In REP mode the 16-bit counter can be used as a

residual counter. In this mode the board can support

unlimited transfer sizes. Once armed, the residual

counter is used to count the actual number of

half-full FIFO transfers.

1

1

In REP mode the 16-bit counter can be used as a

residual counter. In this mode the CIO-PDMA32

can support unlimited transfer sizes. Once armed,

the residual counter is used to count the actual

number of samples.

0

1

In REP mode this configuration can be used when

the transfer size is less than 16.7 Mbytes and an

integer multiple of 256 bytes. The 16-bit counter is

used to count the number of half-full FIFO transfers.

0

0

In REP mode this configuration can be used when

the transfer size is less than 65536 bytes. The 16-bit

counter is used to count the actual number of

samples.

0

0

Comments

HALF_FF_CNT

_REP_CONT

19