Measurement Computing CIO-PDMAxx User Manual

Page 14

The DMA control register is cleared on power-up or hardware reset. If you are

writing your own DMA routine, the DMA enable bit should be set before enabling the

8237 mask register.

DMA level selected by the DMA LEVEL bit is tri-stated when DMA ENABLE = 0.

Take care when writing to AUX1 and AUX2 that the current contents of the DMA

REGISTER are not disturbed.

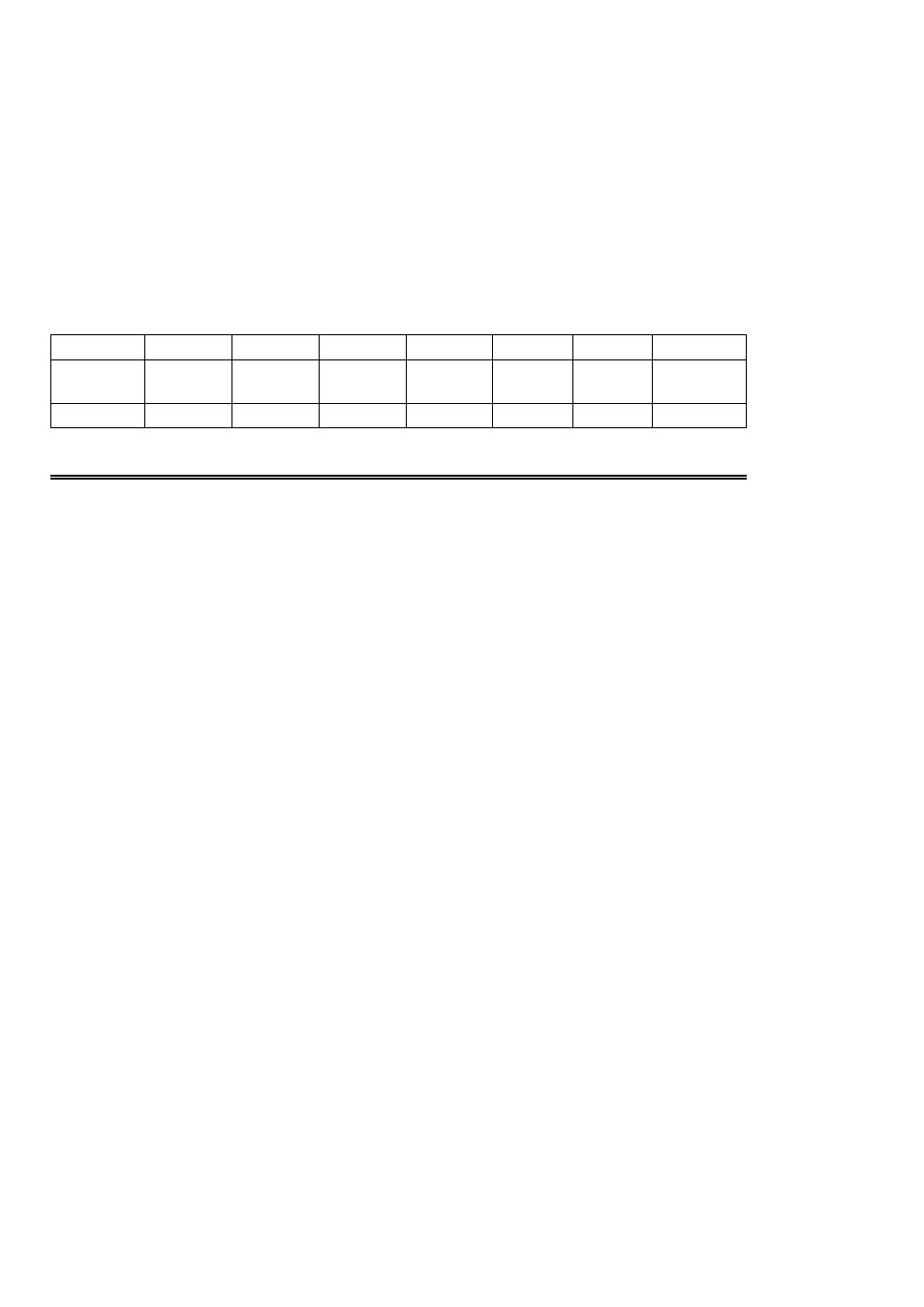

5.1.3 INTERRUPT CONTROL REGISTER

Interrupt control

BASE ADDRESS + 3

302h, 770

10

N/A

N/A

N/A

Pin 26

N/A

N/A

N/A

N/A

SLOPE

INT

SRC

INT

SRC

AUX 3

IR LEV

IR LEV

IR LEV

INT

ENABLE

0

1

2

3

4

5

6

7

Negative edge

1

Positive edge

0

SLOPE

8237 terminal count

11

8254 timer

10

8237 terminal count

01

External input

00

INT SRC (SOURCE)

Output only on pin 26

X

AUX 3

Level 7

111

Level 6

110

Level 5

101

Level 4

100

Level 3

011

Level 2

010

Inactive

001

Inactive

000

IR LEVEL

Enabled

1

Disabled

0

INT ENABLE

FUNCTION

VALUE

BIT NAME

The interrupt control register is cleared on power-up or hardware reset. If you are

writing your own interrupt routine, set the interrupt enable bit before enabling the

8259 mask register. The interrupt level selected by the IR LEVEL bit is tri-stated

when IR ENABLE = 0.

When writing to AUX1 and AUX2, take care not to disturb the current contents of the

INTERRUPT REGISTER.

10