Measurement Computing CIO-PDMAxx User Manual

Page 22

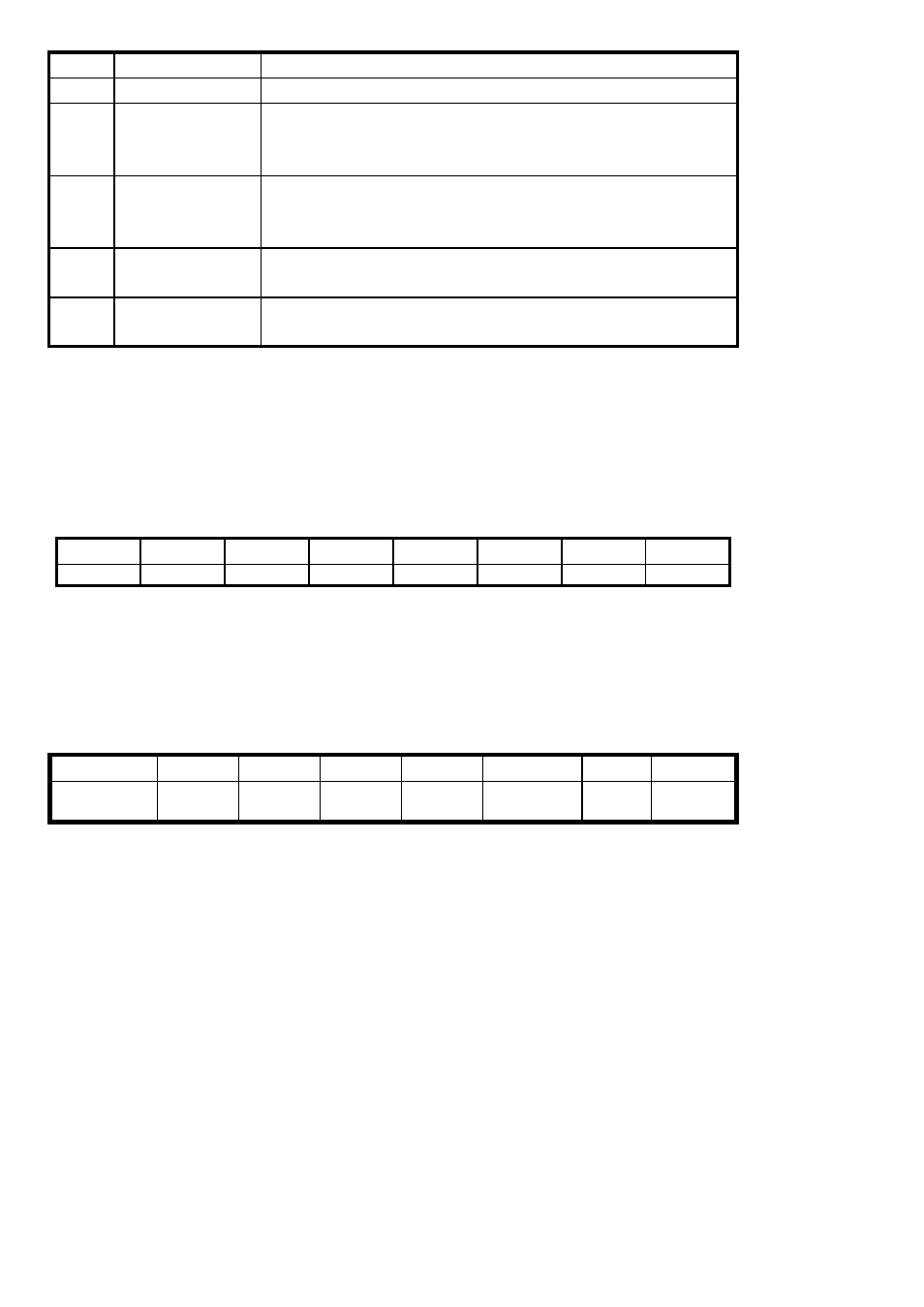

This bit is set when in REP_ENB mode, and the Sample

Counter has reached terminal count.

REP_DONE

0

This bit is set when in REP_ENB mode and the FIFO is

half-full.

REP_FLG

1

This bit is set when in REP_ENB mode and the FIFO

has been overrun. This flag indicates that the FIFO is

being loaded too quickly

OVERRUN

2

This bit is set when in REP_ENB mode and the FIFO

has been underrun. This flag indicates that the FIFO is

being unloaded too quickly.

UNDERRUN

3

1=Interrupt Pending, 0 = No Interrupt

IRQ

7

Description

Name

Bit

5.2.9 FIFO Clear Start Address Register

This is a write only register. A write to this register clears the FIFO address pointers to

zero. Data is don’t care. Prior to initiating a REP-STRING transfer the FIFO write and

read address pointers should always be cleared to a start address of 0.

Base Address + Bh

X

X

X

X

X

X

X

X

0

1

2

3

4

5

6

7

MSB

LSB

5.2.10 REP String Control Register

This is a read/write register. These bits are in the inactive reset state after power-up.

Base Address + Ch

x

x

ERR_ENB

DBL_

BUFF

HALF_

FF_CNT

REP_

CONT

REP_

ENB

REP_

MODE

0

1

2

3

4

5

6

7

MSB

LSB

18