Measurement Computing CIO-PDMAxx User Manual

Page 19

2.

If word mode is selected for regular I/O (D2 = 1), then the B direction bit is

ignored. Both ports operate as a single 16-bit port with the direction set by A

direction bit D0.

3.

The XFERSRC bit is used in both REP and DMA modes to select the transfer

clock source.

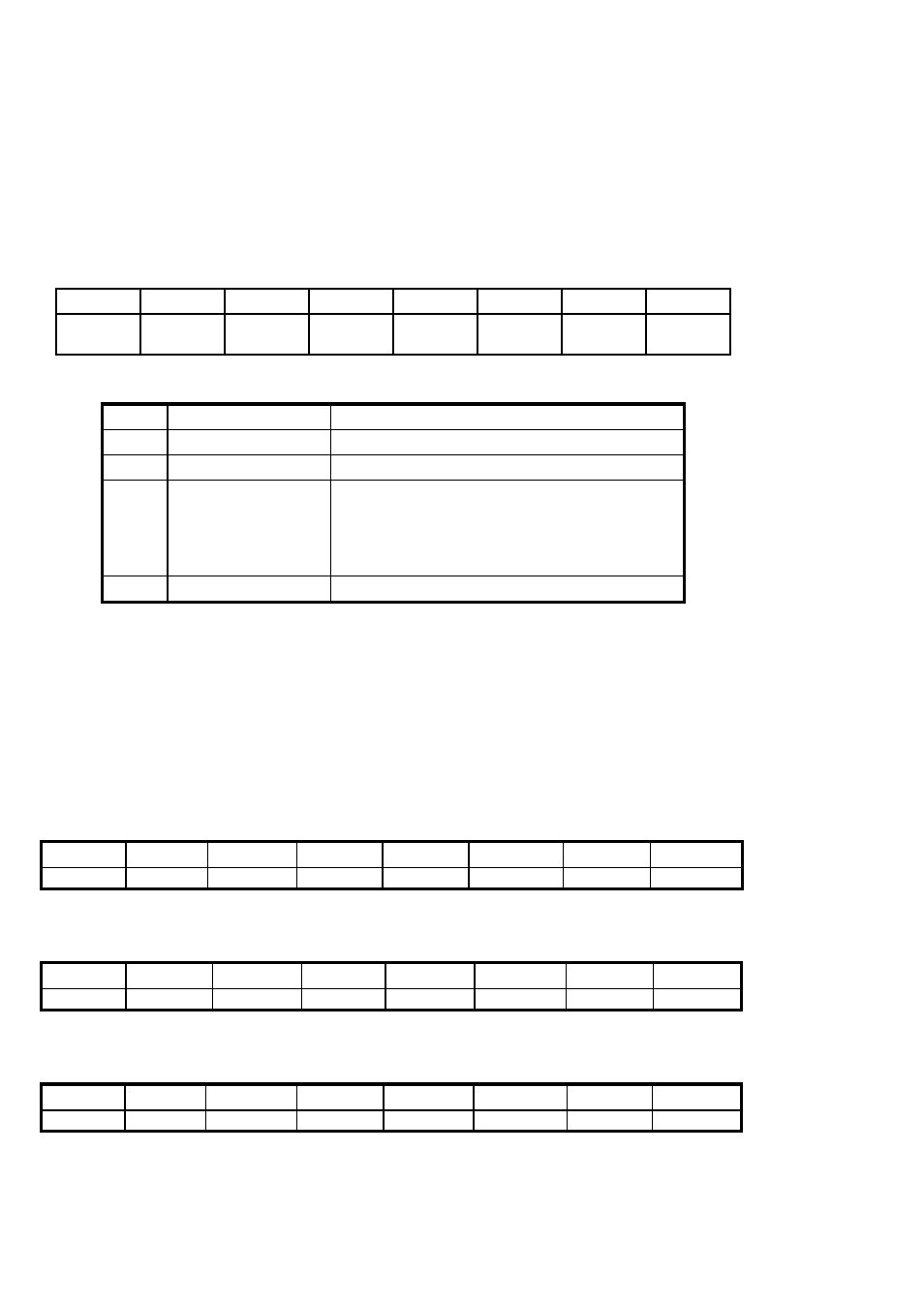

5.2.3 Interrupt Control Register

The interrupt Control Register is an 8-bit read/write register.

Base Address + 3

LSB

MSB

SLOPE

INT

SRC0

INT

SRC1

AUX3

0

0

0

INT

ENB

0

1

2

3

4

5

6

7

0 = + Edge 1 = - Edge

SLOPE

0

00 = External Input

01 = 8237 Terminal Count

10 = Counter/Timer Terminal Count

11 = 8237 Terminal Count

INTSRC(1:0)

2:1

Auxiliary user output

AUX3

3

0 = Disable, 1 = Enable

INTENB

7

Description

Name

Bit

Notes:

1.

The Interrupt Control Register is cleared on power-up, thus disabling interrupts.

2.

When REP_ENB bit is set, the Interrupt Source automatically defaults to the

Counter/Timer Terminal Count.

5.2.4 Counter Load & Read Registers Base Address + 4, 5, 6, and 7

Counter 0

Base Address + 4

LSB

MSB

D0

D1

D2

D3

D4

D5

D6

D7

0

1

2

3

4

5

6

7

Counter 1

Base Address + 5

LSB

MSB

D0

D1

D2

D3

D4

D5

D6

D7

0

1

2

3

4

5

6

7

Counter 2

Base Address + 6

LSB

D0

D1

D2

D3

D4

D5

D6

D7

0

1

2

3

4

5

6

7

15