Measurement Computing CIO-PDMAxx User Manual

Page 16

RL1 to RL0 are the read and load control bits:

RL1

RL0

OPERATION

0

0

Latch counter.

0

1

Read/load high byte.

1

0

Read/load low byte.

1

1

Read/load low then high byte (word transfer).

M2 to M0 are the counter control operation type bits:

M2

M1

M0

OPERATION TYPE

0

0

0

Change on terminal count.

0

0

1

Programmable one-shot.

0

1

0

Rate generator

0

1

1

Square wave generator

1

0

0

Software triggered strobe.

1

0

1

Hardware triggered strobe.

BCD = 0 then counter data is 16-bit binary. (65,535 max)

BCD = 1 then counter data is 4-decade Binary-Coded-Decimal. (9,999 max)

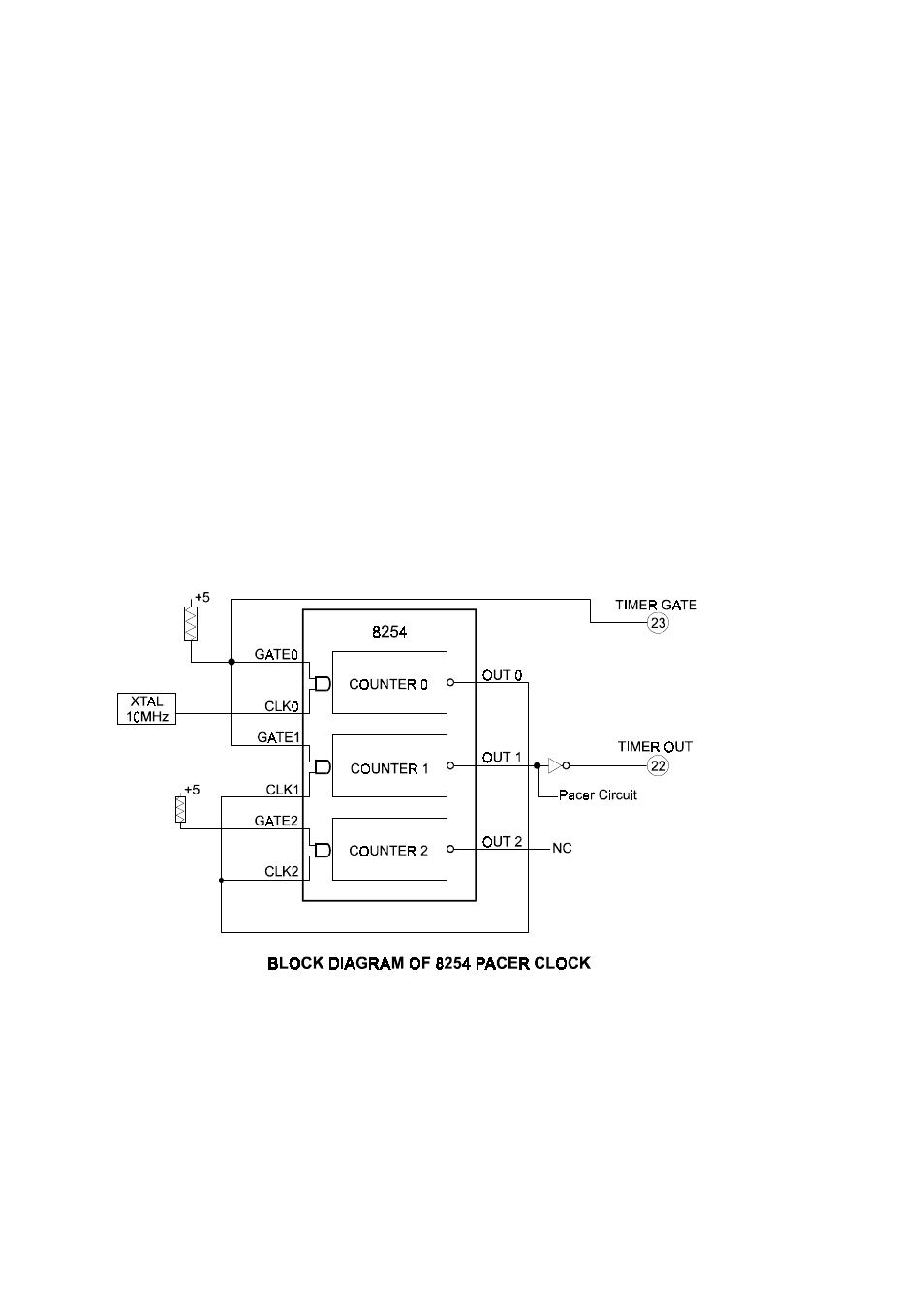

Figure 5-1. Pacer Clock Block Diagram

12

See also other documents in the category Measurement Computing Hardware:

- ACC-300 (7 pages)

- AI-EXP32 (20 pages)

- AI-EXP48 (19 pages)

- BTH-1208LS (30 pages)

- 6K-ERB08 (32 pages)

- BTH-1208LS Quick Start (4 pages)

- 6K-SSR-RACK08 (33 pages)

- BTH-1208LS-OEM (27 pages)

- CB-COM-Digital (68 pages)

- CB-7018 (68 pages)

- CB-7000 Utilities (44 pages)

- CB-7080D (74 pages)

- CB-COM-7033 (44 pages)

- CB-COM-7017 (72 pages)

- CB-COM-7024 (76 pages)

- CB-NAP-7000P (36 pages)

- CIO-DAC02/16 (16 pages)

- CIO-DAC02 (18 pages)

- CB-NAP-7000D (56 pages)

- CIO-DAC16-I (16 pages)

- CIO-DAC16/16 (20 pages)

- CIO-DAS08 (21 pages)

- CIO-DAC16 (20 pages)

- CIO-DAS08/JR (16 pages)

- CIO-DAS08/JR/16 (14 pages)

- CIO-DAS08/JR-AO (16 pages)

- CIO-DAS08-AOM (32 pages)

- CIO-DAS08-PGM (28 pages)

- CIO-DAS16/330 (34 pages)

- CIO-DAS48-I (17 pages)

- CIO-DAS16/M1 (38 pages)

- CIO-DAS48-PGA (18 pages)

- CIO-DAS800 (20 pages)

- CIO-DAS802/16 (22 pages)

- CIO-DAS6402/16 (40 pages)

- CIO-DAS-TEMP (20 pages)

- CIO-DDA06/16 (18 pages)

- CIO-DDA06/JR (17 pages)

- CIO-DIO24H (20 pages)

- CIO-DIO24/CTR3 (21 pages)

- CIO-DI192 (24 pages)

- CIO-DDA06 (21 pages)

- CIO-DIO48 (19 pages)

- CIO-DO192H (16 pages)

- CIO-DIO192 (20 pages)