Measurement Computing CIO-PDMAxx User Manual

Page 21

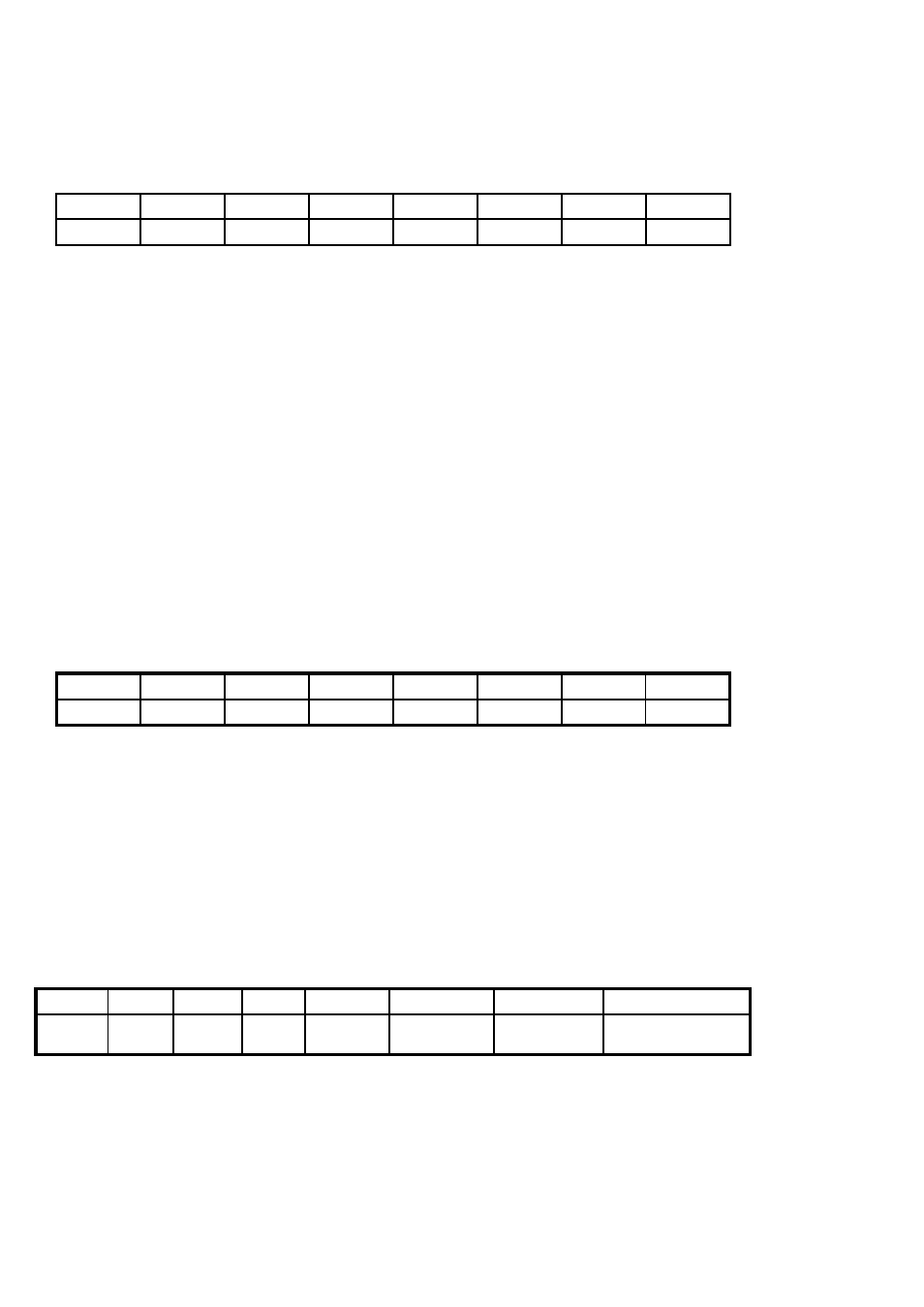

5.2.6 DMA Level Select Register

The level of DMA request generated by the board is determine via this register. This

register is also used to determine the port width during REP mode. This is a read/write

register. These bits are cleared after reset. Note that the unused bits D7:D3 are still

user programmable.

Base Address + 8

LSB

MSB

L0

L1

L2

x

x

x

x

x

0

1

2

3

4

5

6

7

L2, L1, L0 select the DMA level or REP Port size as follows:

000 = Level 0 (byte)

100 = Illegal

001 = Level 1 (byte)

101 = Level 5 (word)

010 = Level 2 (byte)

110 = Level 6 (word)

011 = Level 3 (byte)

111 = Level 7 (word)

x = don’t care

5.2.7 Interrupt Level Register

This is a read/write register used to program the desired interrupt level of the

PDMA-32 board. These bits are cleared after reset. Note that the unused bits D7:D4

are user programmable. Interrupt priorities highest-to-lowest are 9, 10, 11, 12, 14, 15,

3, 4, 5, 6, and 7. There is no interrupt Level 2 on the PC/AT; it is redirected through

Interrupt Level 9.

Base Address + 9

I0

I1

I2

I3

x

x

x

x

0

1

2

3

4

5

6

7

MSB

LSB

x = don’t care

5.2.8 Interrupt Status Register

This is a read only register. In DMA mode this register returns a single bit

corresponding to the state of the PDMA-32’s internal interrupt request. In REP mode

this register provides additional flag information regarding the status of the current

REP transfer. Reading the Interrupt Status Register will clear the pending interrupt

request and re-enable interrupts.

Base Address + Ah

REP_DONE

REP_FLG

OVERRUN

UNDER

RUN

0

0

0

IRQ

0

1

2

3

4

5

6

7

MSB

LSB

17