Measurement Computing CIO-PDMAxx User Manual

Page 13

Ports A & B are set to input on power-up or hardware reset of the computer. The

direction of transfer, input/output, is controlled by one bit for each port in BASE + 2.

The inputs of the ports are one TTL load. The outputs can sink 24mA on output low. .

When the ports are configured for output and a read back is executed, the actual data

on the pins is read back. This may differ from what was written to the port if a chip is

faulty or a digital line is short circuited.

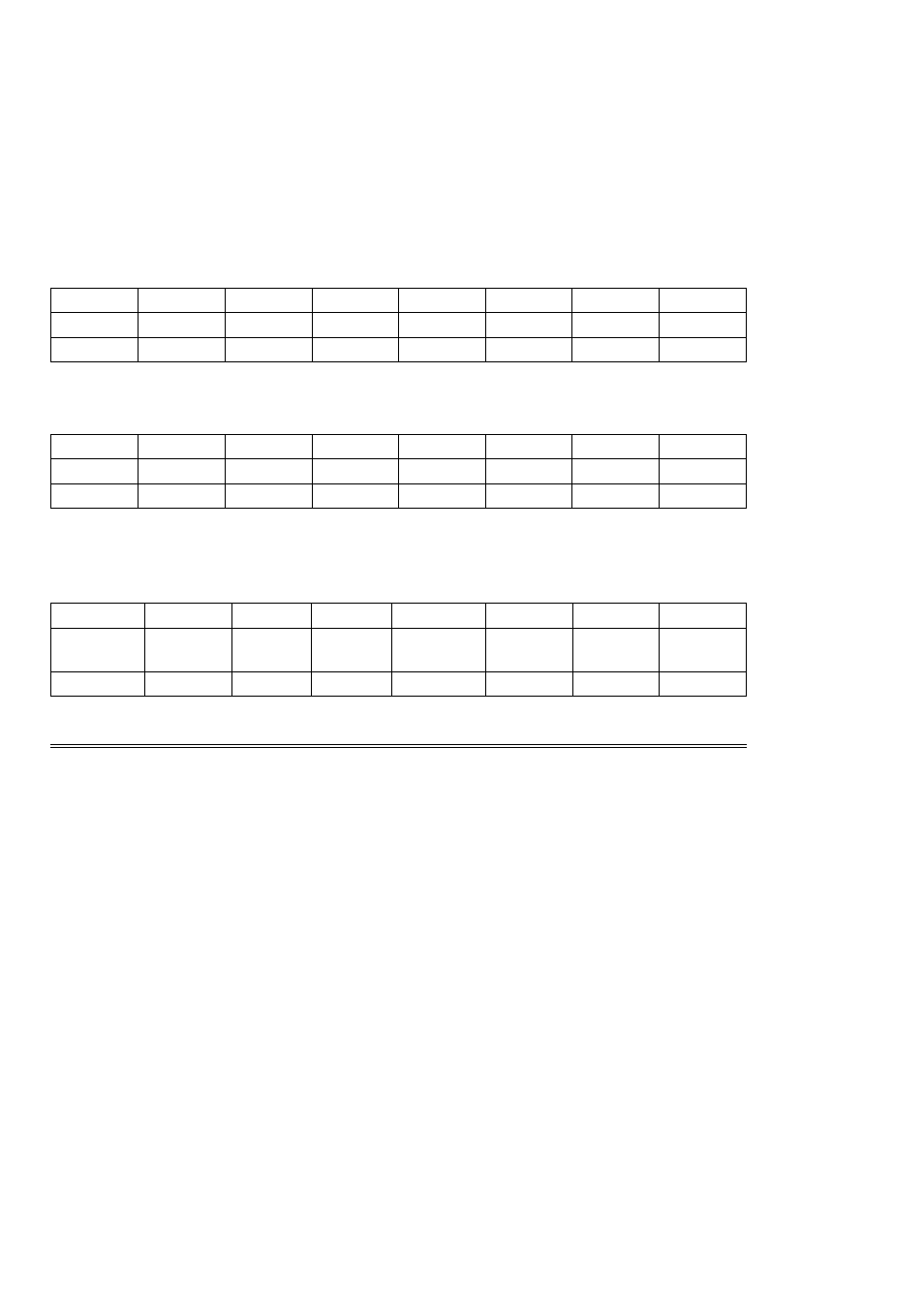

PORT A DATA

BASE ADDRESS + 0

300h, 768

10

Pin 19

Pin 18

Pin 17

Pin 16

Pin 15

Pin 14

Pin 13

Pin 12

A0

A1

A2

A3

A4

A5

A6

A7

0

1

2

3

4

5

6

7

PORT B DATA

BASE ADDRESS + 1

301h, 769

10

Pin 11

Pin 10

Pin 9

Pin 8

Pin 7

Pin 6

Pin 5

Pin 4

B0

B1

B2

B3

B4

B5

B6

B7

0

1

2

3

4

5

6

7

5.1.2 DMA CONTROL REGISTER

DMA control

BASE ADDRESS + 2

302h, 770

10

Pin 37

Pin 29

N/A

N/A

Pin 24

Pin 25

N/A

N/A

PORT A

DIR

PORT B

DIR

BYTE/

WORD

XFER

SOURCE

AUX1

AUX2

DMA

LEVEL

DMA

ENABLE

0

1

2

3

4

5

6

7

Output

1

Input

0

PORT A DIR

Output

1

Input

0

PORT B DIR

Word transfers

1

Byte transfers

0

BYTE/WORD

Internal - 8254 timer

1

External - from Transfer Req In, pin 2.

0

XFER SOURCE

Output only on pin 24

X

AUX1

Output only on pin 25

X

AUX2

Level 3 (channel 3)

1

Level 1 (channel 1)

0

DMA LEVEL

Enabled

1

Disabled

0

DMA ENABLE

FUNCTION

VALUE

BIT NAME

9