Table 4-3 – Artesyn COMX-P40x0 ENP2 Installation and Use (August 2014) User Manual

Page 63

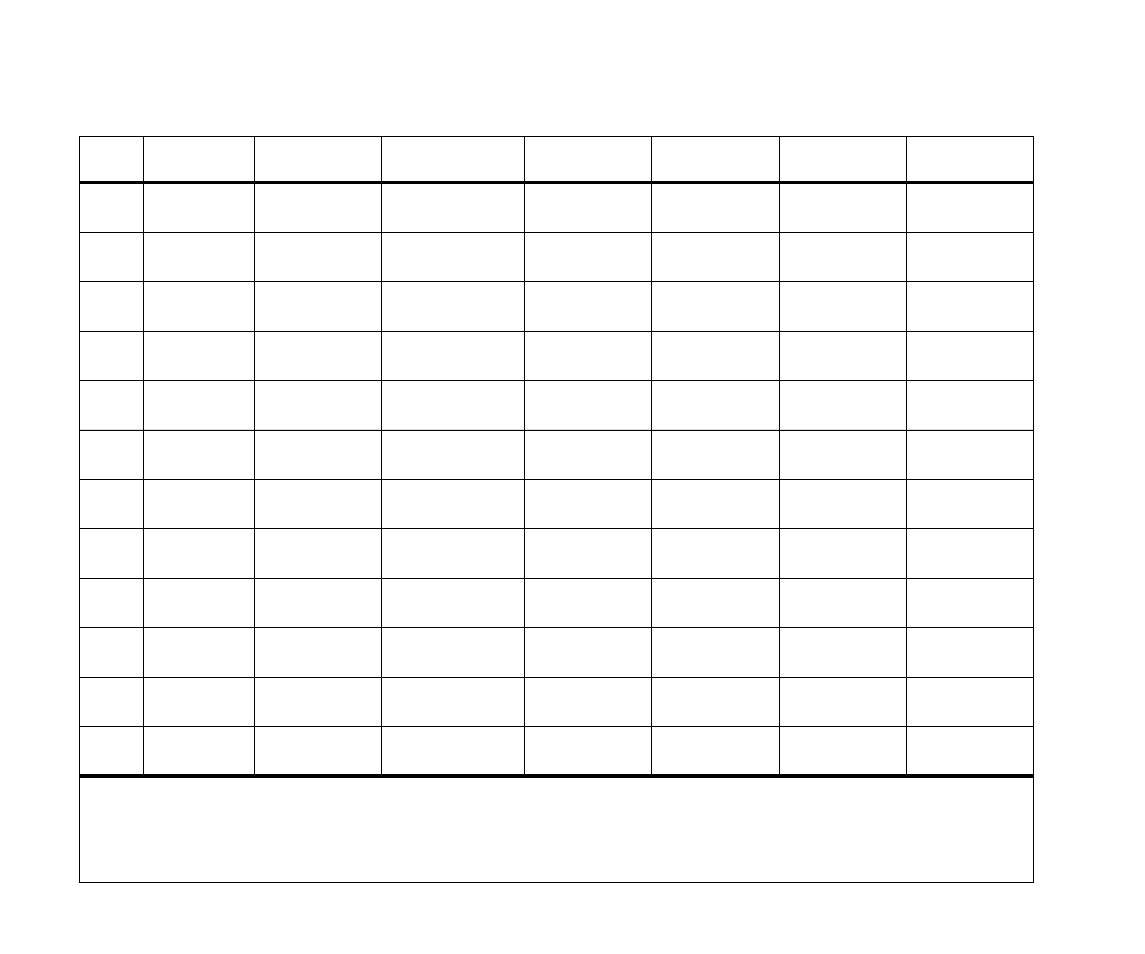

The protocol running on each lane or group of lanes routed to the COM Express connector is configured by the RCW.

Available options are shown in the following table (slot numbers refer to COMX-CAR-P1 PCIe connector slots):

Table 4-3 Options of the SERDES routed to COM Express Connectors

Option

Bank1 SerDes

0-3 (SLOT J6)

Bank1 SerDes 4-7

(SLOT J14)

Bank2 SerDes 10-13

(SLOT J10)

Bank3 SerDes 14-

17 (Slot J2)

4

RCW

[SRDS_PRTCL]

Bank 1 SerDes

Clock3

Bank 2/3 SerDes

Clock3

1

PCIe1 x4

(2.5Gbps)

PCIe2 x4

(2.5Gbps)

XAUI FM2

(3.125Gbps)

1

XAUI FM1

(3.125Gbps)

1

0x05

100MHz

3

125MHz

3

2

PCIe1 x4

(2.5Gbps)

PCIe2 x4

(5Gbps)

XAUI FM2

(3.125Gbps)

1

XAUI FM1

(3.125Gbps)

1

0x05

100MHz

3

125MHz

3

3

PCIe1 x4

(5Gbps)

PCIe2 x4

(2.5Gbps)

XAUI FM2

(3.125Gbps)

1

XAUI FM1

(3.125Gbps)

1

0x05

100MHz

3

125MHz

3

4

PCIe1 x4

(5Gbps)

PCIe2 x4

(5Gbps)

XAUI FM2

(3.125Gbps)

1

XAUI FM1

(3.125Gbps)

1

0x05

100MHz

3

125MHz

3

5

PCIe1 x4

(2.5Gbps)

SGMII FM2 x4

(1.25Gbps)

XAUI FM2

(3.125Gbps)

1

Reserved

2

0x0F

100MHz

3

125MHz

3

6

PCIe1 x4

(2.5Gbps)

SGMII FM2 x4

(1.25Gbps)

XAUI FM2

(3.125Gbps)

1

Reserved

2

0x0F

100MHz

3

125MHz

3

7

SRIO2 x4

(3.125Gbps)

SRIO1 x4

(3.125Gbps)

PCIe3 x4

(2.5Gbps)

1

SGMII FM1 x4

(1.25Gbps)

1

0x19

125MHz

3

100MHz

3

8

SRIO2 x4

(3.125Gbps)

SRIO1 x4

(3.125Gbps)

PCIe3 x4

(5Gbps)

1

SGMII FM1 x4

(1.25Gbps)

1

0x19

125MHz

3

100MHz

3

9

SRIO2 x4

(2.5Gbps)

SRIO1 x4

(2.5Gbps)

XAUI FM2

(3.125Gbps)

1

XAUI FM1

(3.125Gbps)

1

0x13

100MHz

3

125MHz

3

10

SRIO2 x4

(3.125Gbps)

SRIO1 x4

(3.125Gbps)

SGMII FM2 x4

(1.25Gbps)

1

SGMII FM1 x4

(1.25Gbps)

1

0x16

125MHz

3

125MHz

3

11

PCIe1 x4

(2.5Gbps)

SRIO1 x4

(2.5Gbps)

XAUI FM2

(3.125Gbps)

1

XAUI FM1

(3.125Gbps)

1

0x22

100MHz

3

125MHz

3

12

PCIe1 x4

(5Gbps)

SRIO1 x4

(2.5Gbps)

XAUI FM2

(3.125Gbps)

1

XAUI FM1

(3.125Gbps)

1

0x22

100MHz

3

125MHz

3

1 SerDes Bank2 and Bank3 are powered down by default by the RCW, but are later enabled by the firmware.

2 SerDes Bank 3 is unavailable in this configuration.

3 SerDes reference clocks must be properly configured by the carrier or CPU GPIO pins for the selected interfaces to work. See Clock Structure section for clock

settings.

4 Only SerDes lane 14 is routed to Slot J2.