Usb 2.0 mac/phy, Usb 2.0 mac/phy –38 – Altera Cyclone III Development Board User Manual

Page 48

2–38

Chapter 2: Board Components

Communication Ports and Interfaces

Cyclone III 3C120 Development Board Reference Manual

© March 2009 Altera Corporation

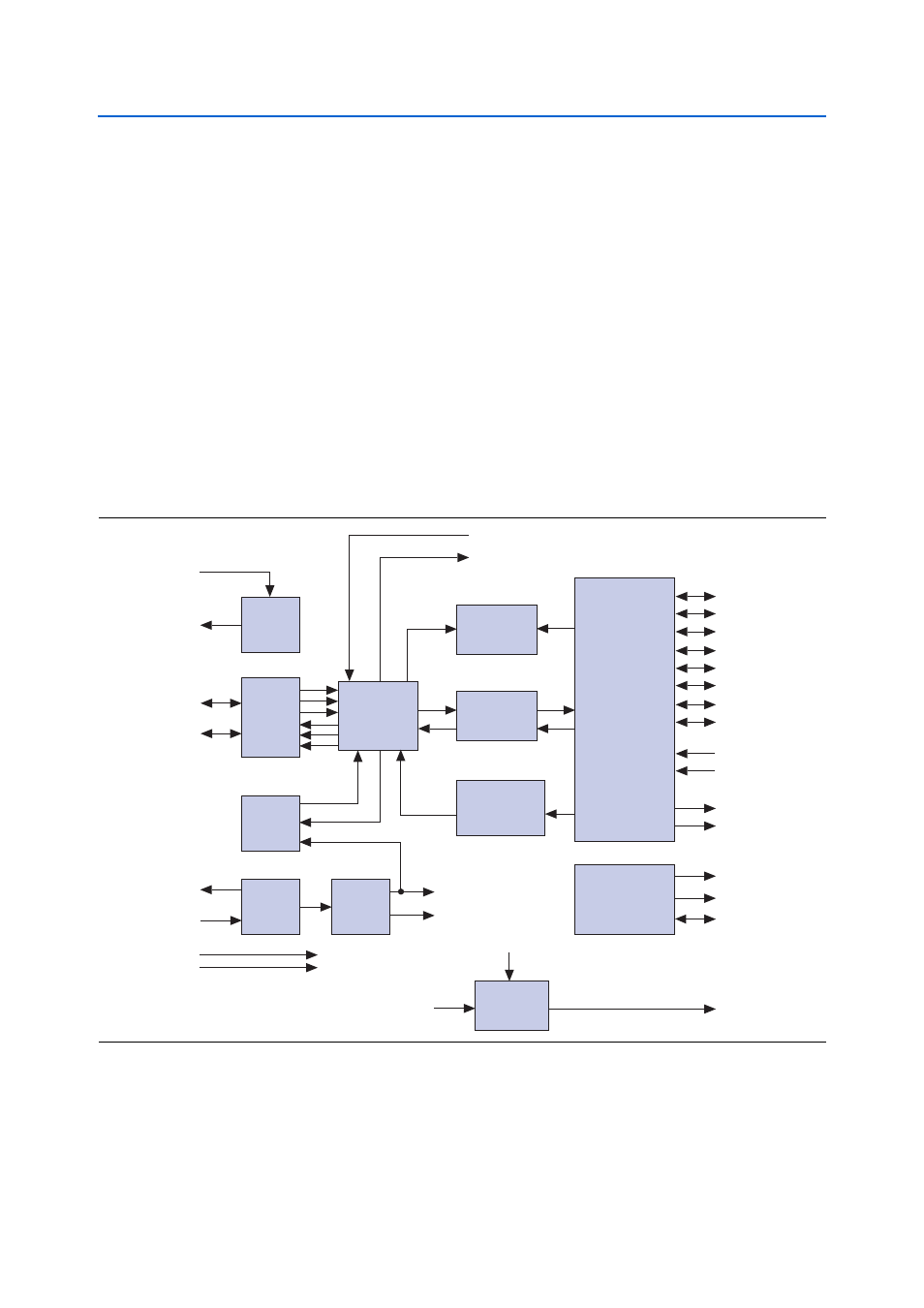

USB 2.0 MAC/PHY

The board incorporates the FTDI USB 2.0 PHY chip. The FT245BL (LQFP package)

provides an easy cost-effective method of transferring data to/from a peripheral and

a host PC at up to 8 million bits (1 Megabyte) per second (Mbps). The simple,

FIFO-like design makes interfacing easier.

The device interfaces to J3, a Type B USB connector similar to those used by common

peripherals such as digital cameras and printers. The maximum speed of the interface

is 12 Mbps. Typical application speeds are around 1.5 Mbps; however, actual system

speed may vary.

The primary usage for the USB device is to provide JTAG programming of on-board

devices such as the FPGA and flash memory. The interface is also the default means

through which the FPGA connects to host PC applications such as SignalTap

®

II,

DSP Builder, and the Nios II JTAG universal asynchronous receiver/transmitter

(UART).

shows the functional block diagram of the FTDI USB PHY device.

f

For more information about the data sheet and related documentation, contact FTDI

at

.

Figure 2–11. FTDI USB PHY Block Diagram

FIFO Transmit

Buffer

384 Bytes

FIFO

Controller

EEPROM

Interface

D0

48MHz

12MHz

D1

D2

D3

D4

D5

D6

D7

EEDATA

RD#

WR

FIFO Receive

Buffer

128 Bytes

USB

Protocol

Engine

USB

Transceiver

3.3V

LDO

Regulator

USB

DPLL

6MHz

Oscillator

x8 Clock

Multiplier

Serial Interface

Engine

(SIE)

RXF#

TXE#

EECS

3V3OUT

EESK

RSTOUT#

RESET#

GND

XTIN

XTOUT

3V3OUT

VCC

USBDM

USBDP

Send Immediate/WakeUP

PWREN#

TEST

Reset

Generator