Altera Cyclone III Development Board User Manual

Page 17

Chapter 2: Board Components

2–7

MAX II CPLD

© March 2009 Altera Corporation

Cyclone III 3C120 Development Board Reference Manual

lists the I/O signals present on the MAX II CPLD. The signal name and

function are relative to the MAX II device.

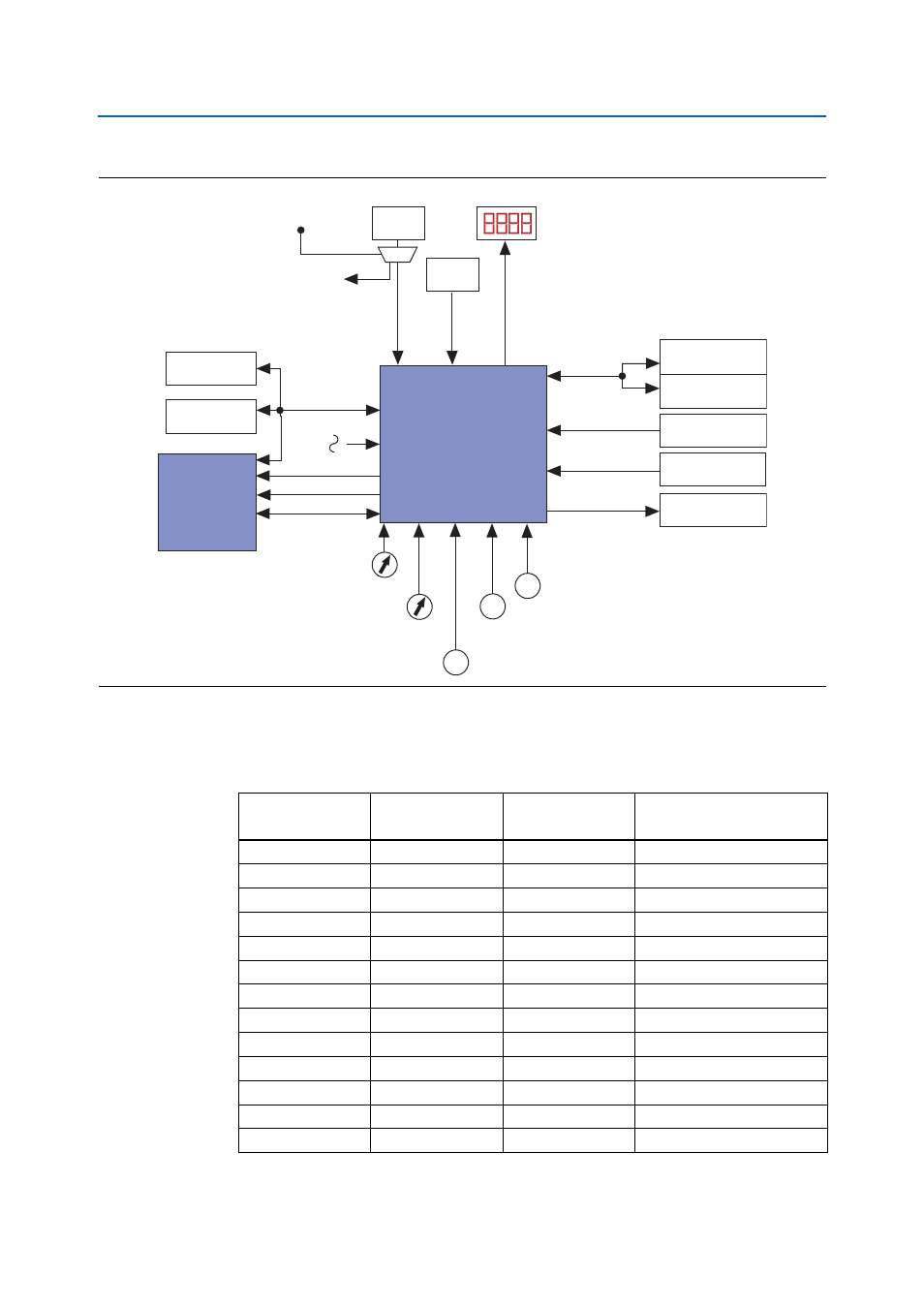

Figure 2–3. MAX II Device’s Block Diagram

Cypress 480 Mbps

USB (x16)

FTDI

12 Mbps USB (x8)

Config Status

LEDs

24 MHz

8-MB

SRAM (x32)

64-MB

Flash (x16)

MAX II CPLD

EPM2210GF256

JTAG

Header

1.8-V CMOS

FSM Bus

MAX II Device

Control DIP Switch

Power Display

RESET_CONFIG

PB CPU_RESET

PB

FACTORY_CONFIG

PB

PWR_SEL

JTAG Control

DIP Switch

Cyclone III

Device

EP3C120F780

PS Config

JTAG Config

USB Data Bus

PGM_CONFIG_SEL

Power

Measure

1.8-V CMOS

1.8-V CMOS

1.8-V CMOS

2.5-V CMOS

2.5

V

CMOS

2.5

V

CMOS

To FPGA

Table 2–5. MAX II Device Pin-Out

MAX II Pin Number

I/O Standard

Signal Direction

Schematic

Signal Name

P3

—

Input

TCK

L6

—

Input

TDI

M5

—

Output

TDO

N4

—

Input

TMS

C14

1.8 V

Output

CLKIN_125_EN

J12

1.8 V

Input

CLKIN_24

E13

1.8 V

Output

CLKIN_50_EN

M9

1.8 V

Input

CPU_RESETn

F11

1.8 V

Input

DEV_SEL

A10

2.5 V

Input

FACTORY_CONFIGn

G13

1.8 V

Output

FLASH_ACTIVE

L15

1.8 V

Output

FLASH_BYTEn

K14

1.8 V

Output

FLASH_CEn