Altera Viterbi Compiler User Manual

Page 6

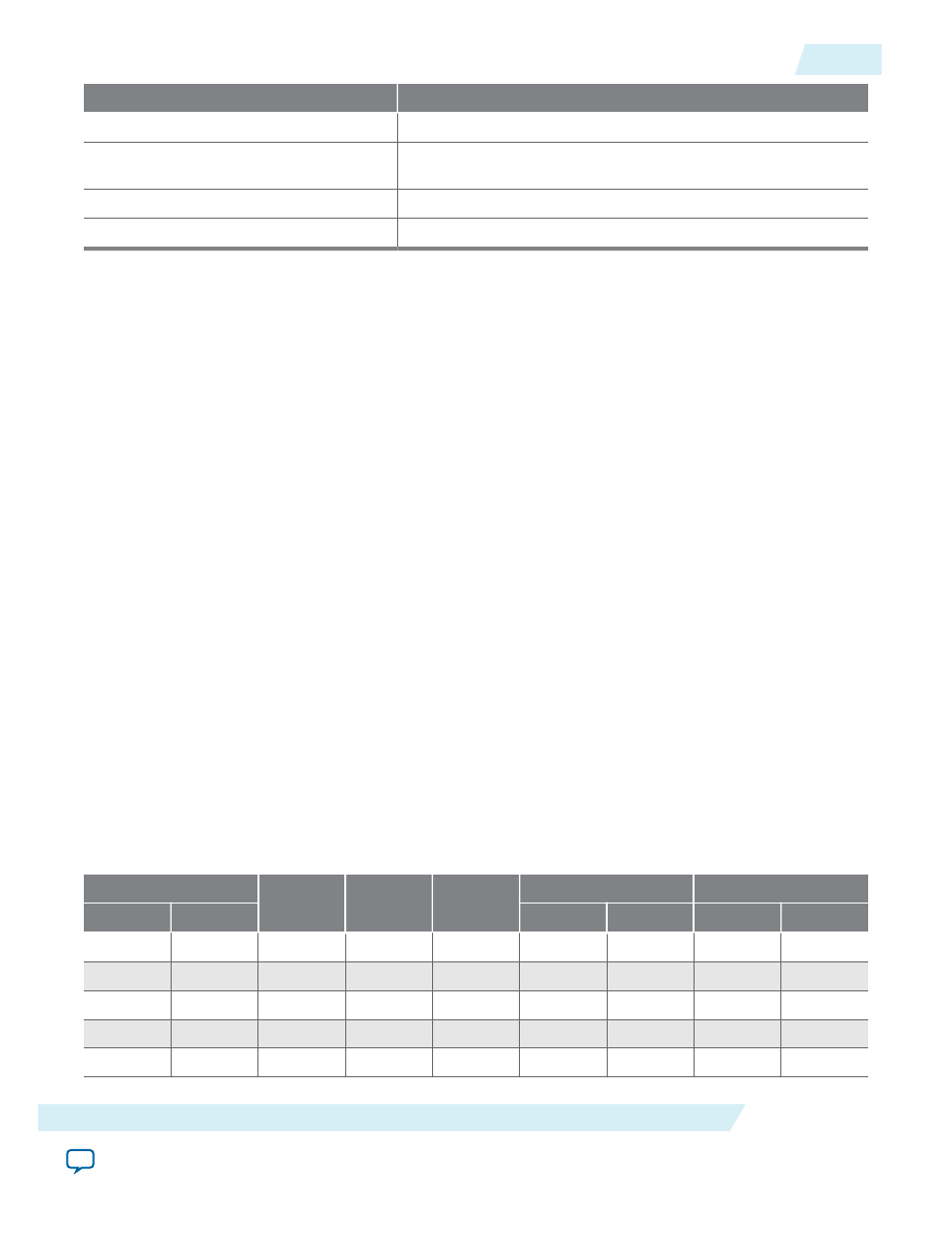

Item

Description

Release Date

December 2014

Ordering Code

IP-VITERBI/HS (parallel architecture) IP-VITERBI/SS (hybrid

architecture)

Product ID

0037 (parallel architecture) 0038 (hybrid architecture)

Vendor ID

6AF7

Altera verifies that the current version of the Quartus II software compiles the previous version of each IP

core. Altera does not verify that the Quartus II software compiles IP core versions older than the previous

version. The Altera IP Release Notes lists any exceptions.

Related Information

•

•

Viterbi IP Core Performance and Resource Utilization

This typical expected performance uses different architectures and constraint length, L, combinations,

and ACS units, A, and the Quartus II software. Performance largely depends on constraint length, L.

Hybrid Architecture

The typical expected performance for a hybrid Viterbi IP core uses the Quartus II software with the Arria

V (5AGXFB3H4F40C4), Cyclone V (5CGXFC7D6F31C6), and Stratix V (5SGSMD4H2F35C2) devices

and the following parameters:

• v = 6 × L

• softbits = 3

• N = 2

where:

• v is the traceback length

• L is the constraint length

• N is the number of coded bits

• A is the number of ACS units

Table 1-3: Typical Performance

Parameters

Device

ALM

f

MAX

(MHz)

Memory

Registers

L

A

M10K

M20K

Primary

Secondary

5

1

Arria 10

401

383

--

3

422

40

5

1

Arria V

323

201

5

--

390

60

5

1

Cyclone V 324

172

5

--

390

53

5

1

Stratix V

316

432

--

5

388

44

7

1

Arria 10

521

370

--

4

559

50

UG-VITERBI

2014.12.15

Viterbi IP Core Performance and Resource Utilization

1-3

About the Viterbi IP Core

Altera Corporation