Trellis decoder, Trellis decoder -4 – Altera Viterbi Compiler User Manual

Page 22

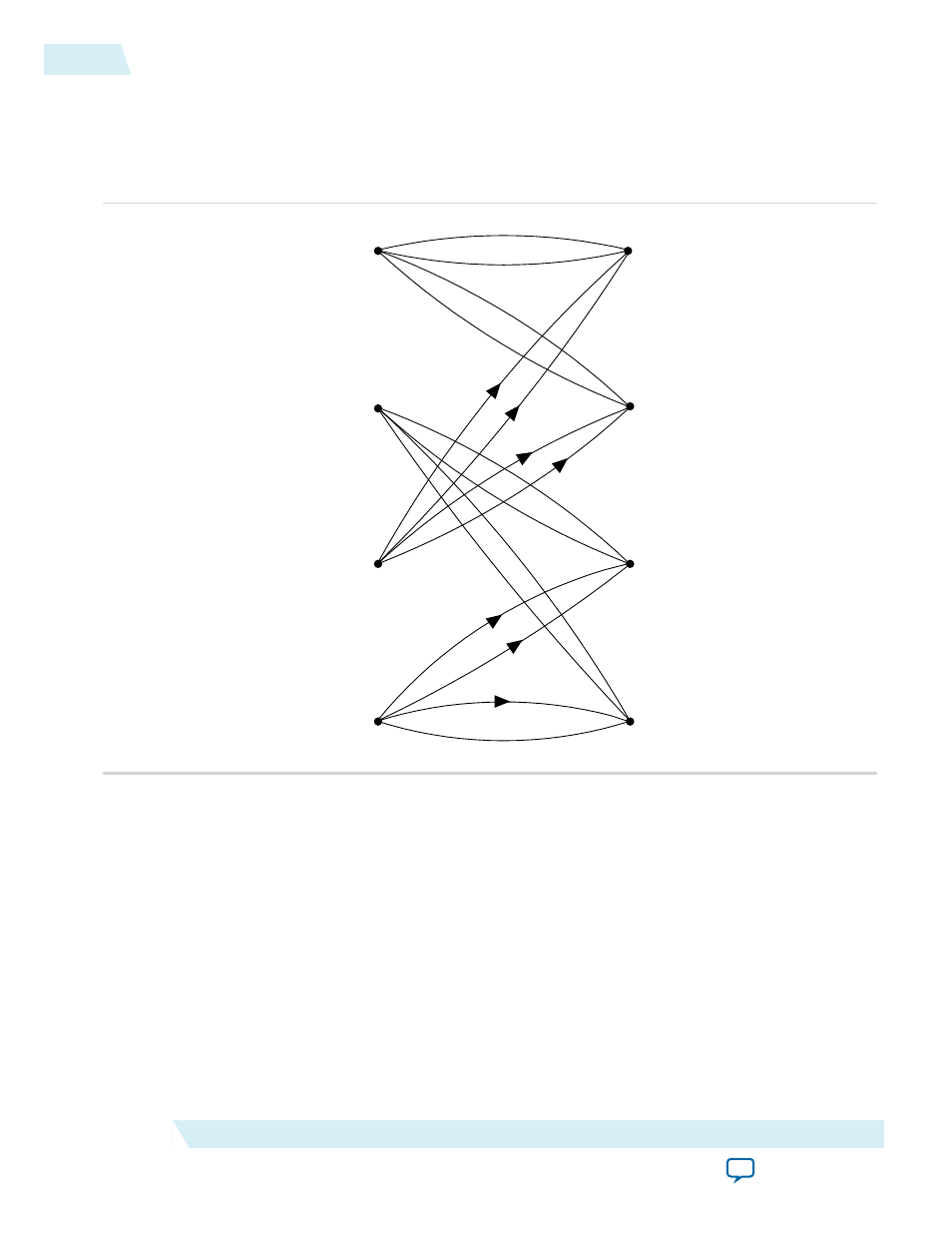

Figure 3-4: Four-State Trellis

The four-state trellis is the trellis for the 1/2 rate convolution encoder with the addition of parallel paths in

each transition to accommodate the uncoded bit c2. The decoder uses the coded bits (c1, c0) to select one

of the four subsets that contain two signal points each It uses the uncoded bit to select one of the two

signal points within each subset.

00

01

10

11

101

001

110

010

000 = (c

2

c

1

c

0

)

011

111

111

011

100

000

100

001

101

010

110

Trellis Decoder

The decoder processes an arriving symbol to obtain four branch metric values and a sector number. The

branch metrics enter the Viterbi decoder in trellis mode and it obtains the encoded bit.

The encoder re-encodes this bit stream and the decoder uses the output of this encoder with the sector

number information to retrieve the uncoded bit. The testbench implements all the logic. The wizard

generates the branch metric values and sector number values, so you need no logic to create these values.

The testbench reads the sector number when it needs it. It has no delay functionality nor rotation. The

wizard-created data introduces has no phase error so the phase is aligned. In a real system, you must

calculate the phase. For a TCM code the BER block does not produce a meaningful output (

numerr

),

because the BER block does not compute errors at the input for TCM codes.

3-4

Trellis Decoder

UG-VITERBI

2014.12.15

Altera Corporation

Viterbi IP Core Functional Description