Restoring the max v cpld to the factory settings – Altera Cyclone V SoC User Manual

Page 15

Chapter 3: Development Board Setup

3–5

Restoring the MAX V CPLD to the Factory Settings

November 2013

Altera Corporation

Cyclone V SoC Development Kit

User Guide

For more information about the FPGA board settings, refer to the

.

Restoring the MAX V CPLD to the Factory Settings

This section describes how to restore the original factory contents to the MAX V

CPLD on the development board. Make sure you have the Nios II EDS installed, and

then perform these steps:

1. Set the board switches to the factory default settings described in

Switch and Jumper Settings” on page 3–1

.

1

DIP switch SW4.4 includes the MAX V device in the JTAG chain.

2. Launch the Quartus II Programmer.

3. Click Auto Detect.

4. Click Add File and select

dir>\kits\cycloneVSX_5csxfc6df31_soc\factory_recovery\max

5. Turn on the Program/Configure option for the added file.

6. Click Start to download the selected configuration file to the MAX V CPLD.

Configuration is complete when the progress bar reaches 100%.

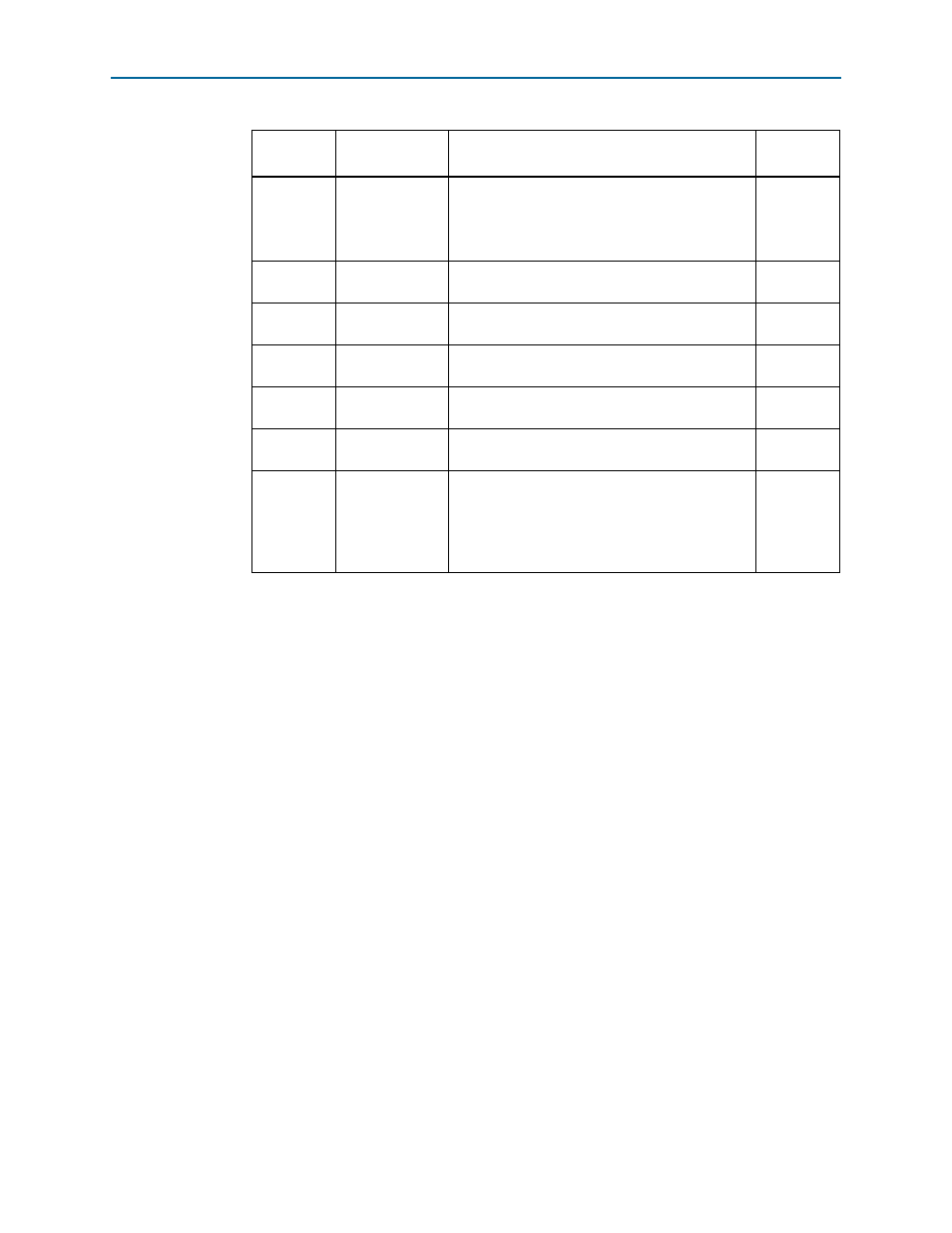

J16

JTAG MIC SEL

■

SHORT: JTAG TRST input to HPS driven from

the JTAG chain.

■

OPEN: JTAG TRST input to HPS driven from the

MICTOR.

OPEN

J26

CLKSEL0

Selects the HPS clock settings.

(

)

SHORT pins

2-3

J27

CLKSEL1

Selects the HPS clock settings.

(

)

SHORT pins

2-3

J28

BOOTSEL0

Selects the boot mode and source for the HPS.

(

SHORT pins

1-2

J29

BOOTSEL1

Selects the boot mode and source for the HPS.

(

SHORT pins

2-3

J30

BOOTSEL2

Selects the boot mode and source for the HPS.

(

SHORT pins

1-2

J31

SPI I2C

■

SHORT: Select SPI bus access from HPS to

Linear Tech daughter card interface through

J32.

■

OPEN: Select I

2

C bus access from HPS to Linear

Tech daughter card interface through J32.

(

OPEN

Note to

:

(1) For more information, refer to the

(2) This connection can be software controlled from the HPS GPIO pin F16 on rev D and later boards.

Table 3–4. Default Jumper Settings (Continued)

Board

Reference

Board Label

Description

Default

Position