Altera Remote Update IP Core User Manual

Page 21

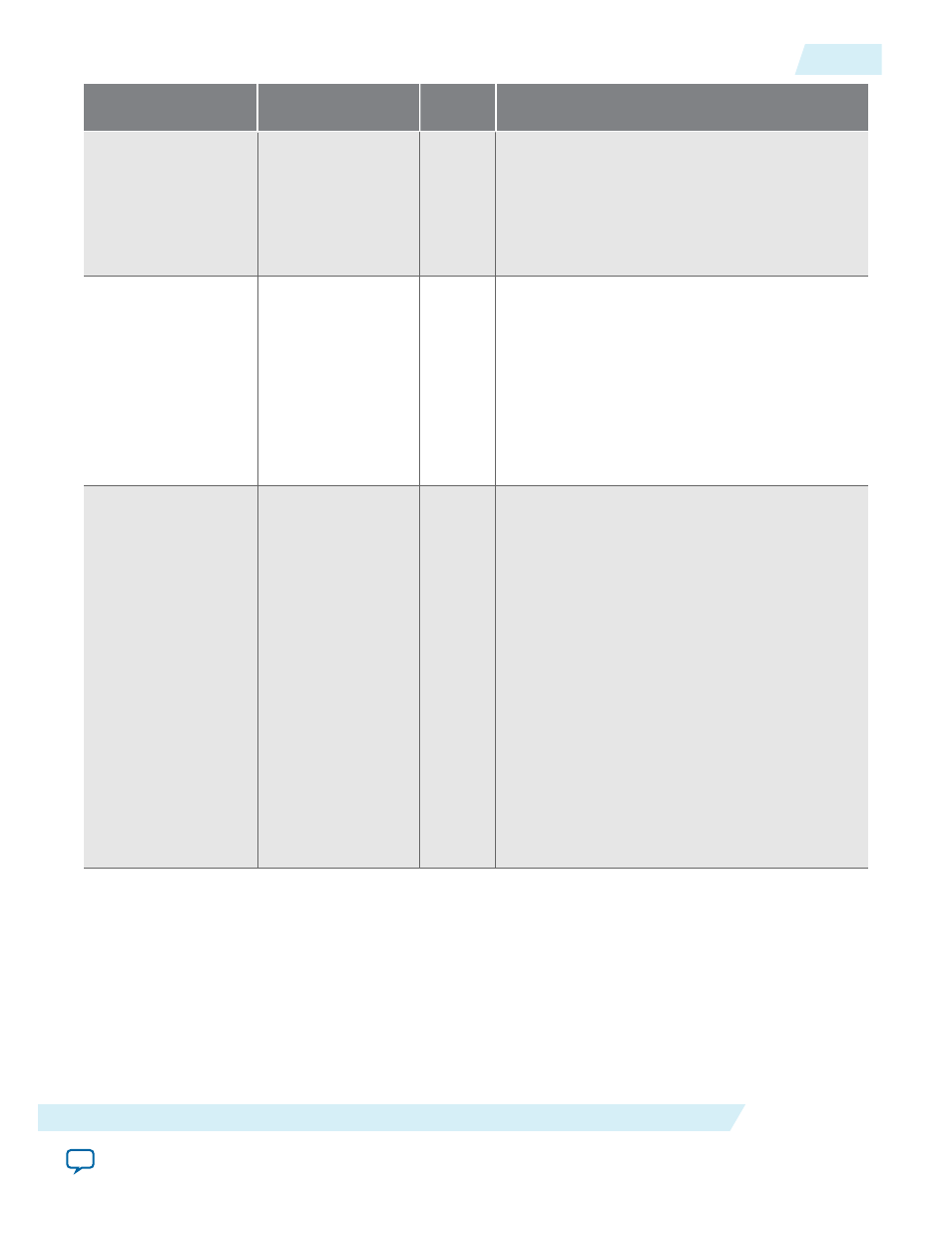

Name

Port

Required

?

Description

reset

Input

Yes

This is an active high signal. Asserting this signal

high will reset the IP core.

Asynchronous reset input to the IP core to

initialize the machine to a valid state. The

machine must be reset before first use, otherwise

the state is not guaranteed to be valid.

busy

Output

No

Busy signal that indicates when remote update

block is reading or writing data.

While this signal is asserted, the machine ignores

most of its inputs and cannot be altered until the

machine deasserts this signal. Therefore, changes

are made only when the machine is not busy.

This signal goes high when

read_param

or

write_param

is asserted, and remains high until

the read or write operation completes.

data_out[]

Output

No

Data output when reading parameters.

This bus holds read parameter data from the

remote update block. The

param[]

value

specifies the parameter to read. When the

read_

param

signal is asserted, the parameter value is

loaded and driven on this bus. Data is valid when

the busy signal is deasserted.

If left unconnected, the default value for the port

is

0

. The width of this bus is device-dependent:

A 24-bit bus width in the Quartus II software

version 13.0 or earlier. For the Quartus II

software version 13.1 and onwards, the bus

widths are as follow:

• 24-bit bus width—using 3-byte addressing

configuration device, for example EPCS128.

• 32-bit bus width—using 4-byte addressing

configuration device, for example EPCQ256.

UG-31005

2015.04.07

Ports

21

Altera Remote Update IP Core User Guide

Altera Corporation