4 agc register description, 1 pci configuration register – Acrosser ACE-MINI User Manual

Page 36

Revision: 1.0

36

3.4 AGC Register Description

ACE-B2019 has one 256KB SRAM and AGC I/O ports from A to J. ACE-B2019A has

two 512KB SRAM and AGC I/O ports from A to L and port XA, XB, it supports to connect to

AR-B2009 for reel control.

This chapter descries the function of the register inside the AGC chip. To program the

application’s software, users need to know these registers.

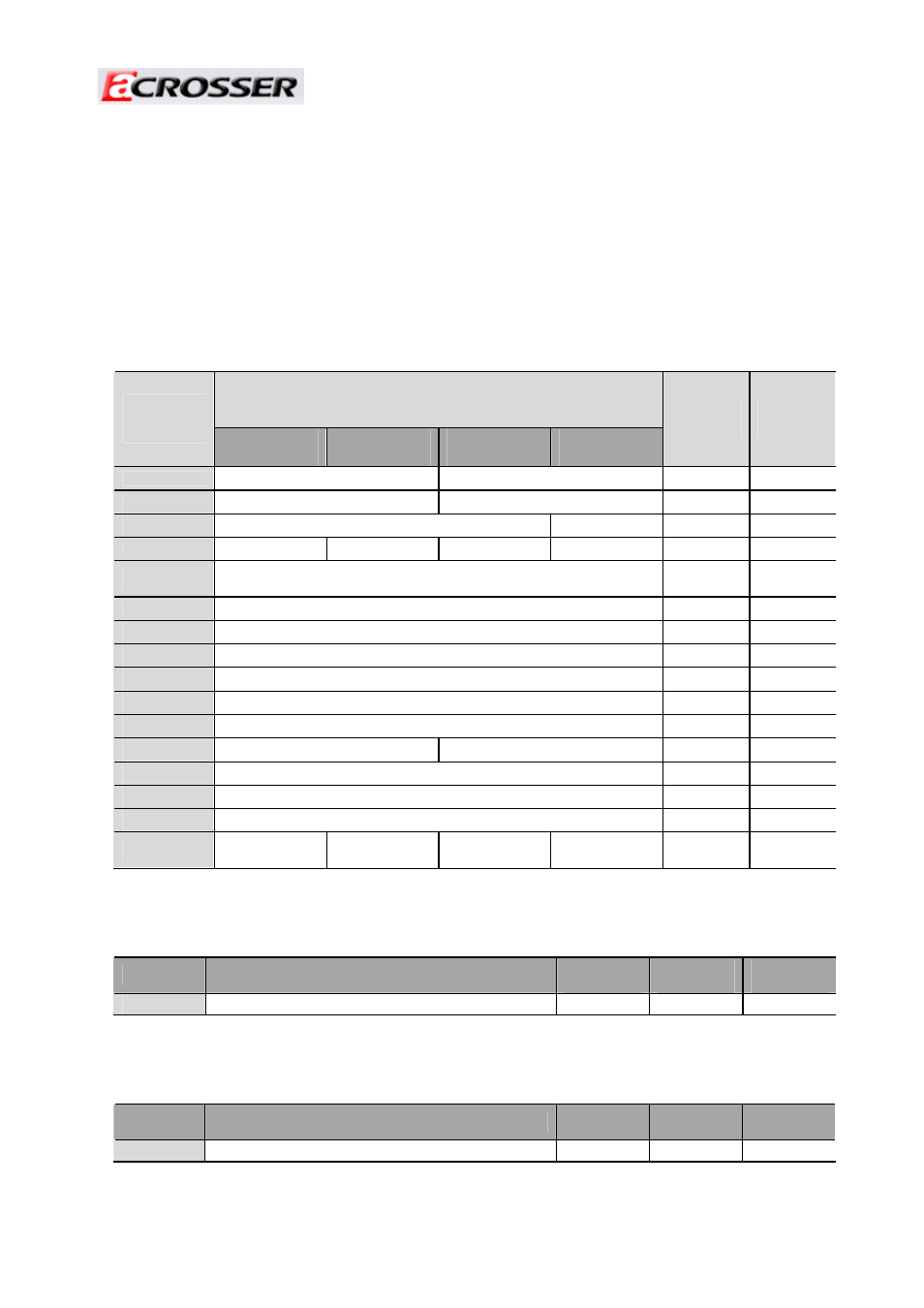

3.4.1 PCI Configuration Register

32 bit Register

PCI CFG

Register Offset

Address

31

24

23

16

15

8

7

0

PCI

Readable

PCI

Writable

00h

Device ID

Vendor ID

Yes

No

04h Status

Command

Yes

No

08h

Class Code

Revision ID

Yes

No

0Ch

BIST

Header Type

Latency Timer

Cache Line Size

Yes

No

10h

PCI Base Address 0 for Memory Mapped Configuration Registers

Yes

es

14h

PCI Base Address 1 for I/O Mapped Configuration Registers

Yes

Yes

18h

PCI Base Address 2 (Not Supported)

No

No

1Ch

PCI Base Address 3 (Not Supported)

No

No

20h

PCI Base Address 4 (Not Supported)

No

No

24h

PCI Base Address 5 (Not Supported)

No

No

28h

Cardbus CIS Pointer (Not Supported)

Yes

No

2Ch

Subsystem ID

Subsystem Vendor ID

Yes

No

30h

PCI Base Address for Local Expansion ROM (Not Supported)

Yes

No

34h Reserved No

No

38h Reserved No

No

3Ch

Max_Lat

Min_Gnt

Interrupt Pin

Interrupt Line

Yes

es / No

Vendor ID Register (00h : 01h)

Bit Field

Description

Software

Readable

Software

Writable

Value after

Reset

15 : 0

Vendor ID. Identifies manufacturer of the device.

Yes

No

1204h

Device ID Register (02h : 03h)

Bit Field

Description

Software

Readable

Software

Writable

Value after

Reset

31 : 16

Device ID. Identifies particular device.

Yes

No

5296h