Opus card – ddr-2 interface – Digilent DDR-2 Opus Card User Manual

Page 6

Opus Card – DDR-2 Interface

Reference Manual

12/03/2010 07:35 AM

6

Copyright © 2009-2010 by CML

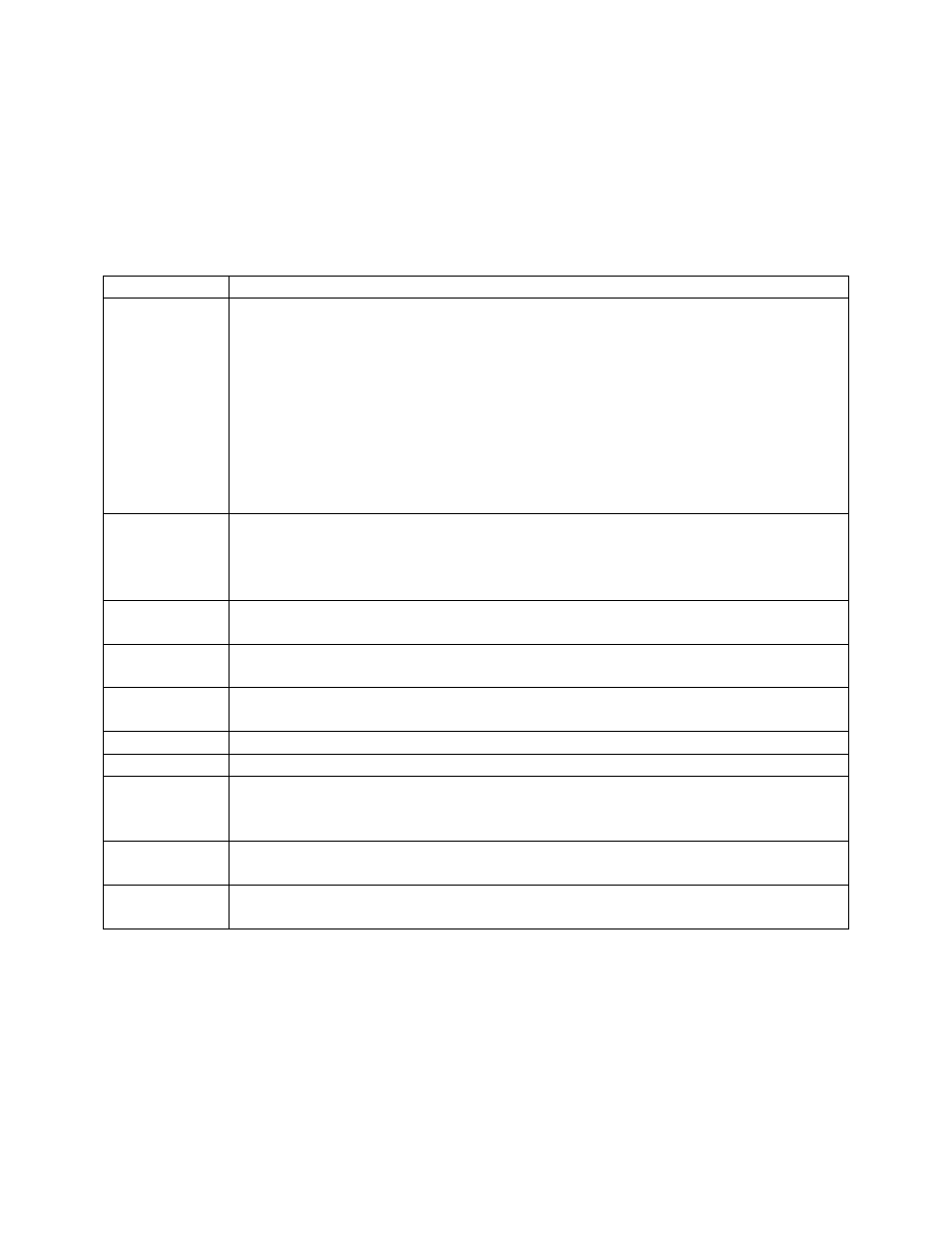

2.2 Write State Machine

The write state machine currently has ten states to support the writing of data to memory.

Transitions from one state to the next occur on the rising edge of DDR2_Clk and the state

machine is synchronously reset to Idle when Bus2IP_Reset is ‘1’. Each state is described below:

State

Description

Idle

Waiting for a write from the PLB slave. A write is detected when Bus2IP_CS is

‘1’, Bus2IP_RNW is ‘0’, App_AF_AFull is ‘0’, and App_WDF_Afull is ‘0’.

The state machine transitions to Wait_Wr_Req on the next clock when these

conditions are met.

This state is also used to pass through needed commands from the read_ctrl

entitiy. The read_ctrl entity generates the Rd_Send_Ack and Rd_Send_Cmd

signals that are used to control the App_AF_Cmd, App_AF_Addr,

App_AF_WREn, IP2Bus_AddrAck, and IP2Bus_RdAck outputs when in this

state.

Wait_Wr_Req Waiting for Bus2IP_WrReq to transition to ‘1’ to indicate the data to be written

to memory is valid. The state machine transitions to the next state when

Bus2IP_WrReq is ‘1’. The next state is Wr_Word1 if Bus2IP_Burst is ‘0’.

Otherwise the next state is Save_W1.

Save_W1

Save word 1 of burst write. The next state is Wr_Word1 when the PLB slave is

configured for 64-bit data width. Otherwise the next state is Save_W2.

Save_W2

Save word 2 of burst write (32-bit PLB bus only). When Bus2IP_Clk is ‘0’, the

next state is set to Save_W3.

Save_W3

Save word 3 of burst write (32-bit PLB bus only). ). When Bus2IP_Clk is ‘0’,

the next state is set to Wr_Brst1.

Wr_Brst1

Write word 1 of burst to DDR-2. The next state is Wr_Brst2.

Wr_Brst2

Write word 2 of burst to DDR-2. The next state is Wr_BrstD.

Wr_BrstD

Delay after burst write to DDR-2. The next state is Save_W1 if the burst write

is not complete (Bus2IP_Burst = ‘1’ and Bus2IP_CS = ‘1’). Otherwise the next

state is Idle.

Wr_Word1

State that writes the low order 64-bit word to memory. The state machine

transitions to Wr_Word2 on the next clock.

Wr_Word2

State that writes the high order 64-bit word to memory. The state machine

transitions to Idle on the next clock.