Opus card – ddr-2 interface – Digilent DDR-2 Opus Card User Manual

Page 14

Opus Card – DDR-2 Interface

Reference Manual

12/03/2010 07:35 AM

14

Copyright © 2009-2010 by CML

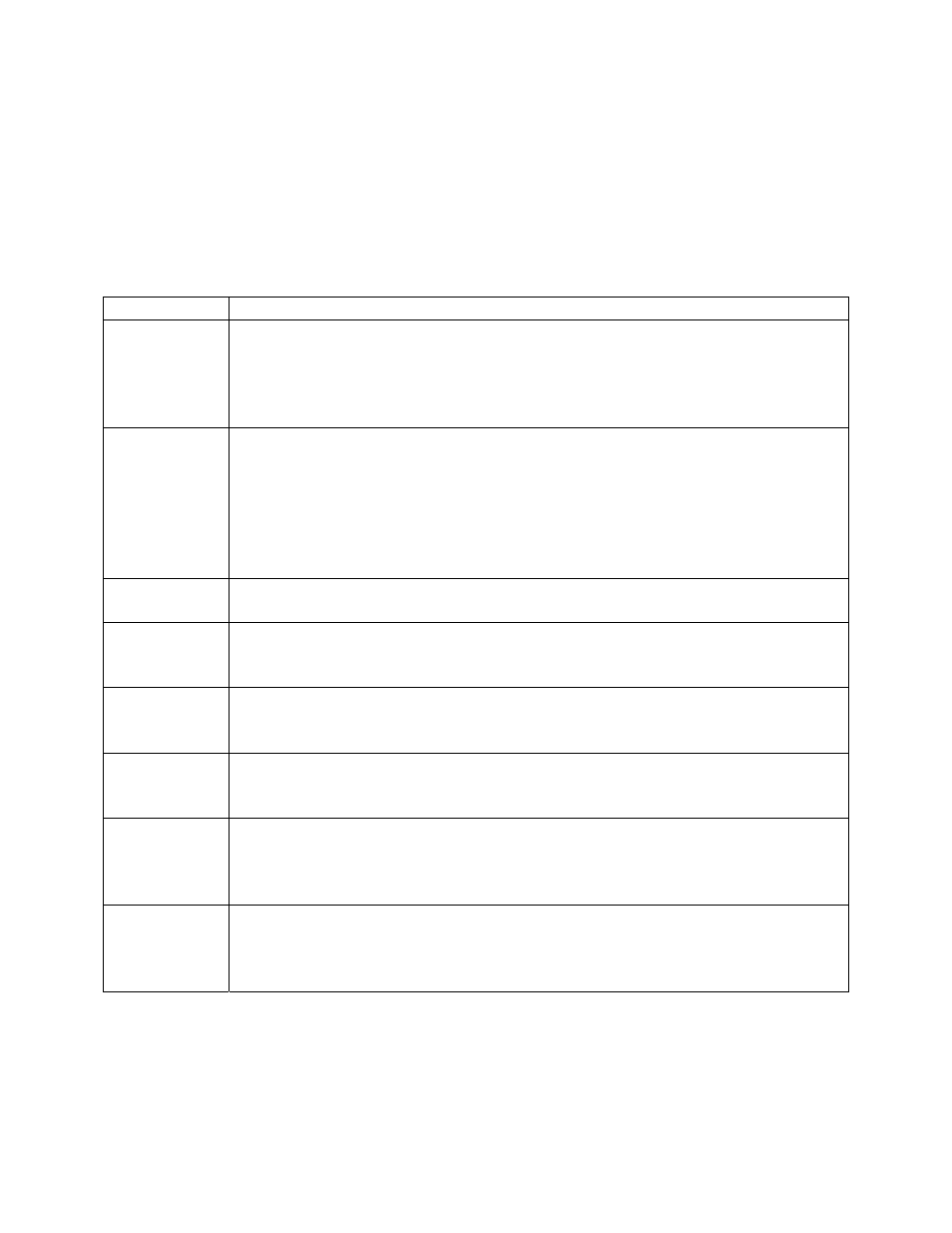

3.2 Read State Machine

The read state machine currently has eight states to support the reading of data from memory via

the DDR-2 memory controller. Transitions from one state to the next occur on the rising edge of

DDR2_Clk and the state machine is synchronously reset to Idle when Bus2IP_Reset is ‘1’. Each

state is described below:

State

Description

Idle

Waiting for a read request from the PLB slave. A read is detected when

Bus2IP_CS is ‘1’, Bus2IP_RdReq is ‘1’, and App_AF_AFull is ‘0’. The state

machine then transitions to Wait_RdValid on the next clock during a non-burst

read. During a burst read, the state machine transitions to Wait_RdValid one

clock after the last address of the burst is queued to the DDR-2 controller.

Wait_RdValid Waiting for Rd_Data_Valid to transition to ‘1’ to indicate the data has been read

from memory and is present on Rd_Data_FIFO_Out. The state machine

transitions to Rd_Align when Bus2IP_Clk is ‘1’ on a non-burst read.

Otherwise, the state machine transitions toRd_Ack1 on a non-burst read.

For a burst-read, the state machine transitions to Queue_D1 when

Rd_Data_Valid is ‘1’.

Rd_Align

Nothing occurs during this state but it does cause the state machine to align with

Bus2IP_Clk. The state machine transitions to Rd_Ack1 on the next clock.

Rd_Ack1

State that acknowledges the read from the PLB slave and places the data for the

requested memory address on IP2Bus_Data. The state machine transitions to

Rd_Ack2 on the next clock.

Rd_Ack2

State that acknowledges the read from the PLB slave and places the data for the

requested memory address on IP2Bus_Data. The state machine transitions to

Idle on the next clock.

Queue_D1

State that indicates the first word has been saved to the FIFO during a burst

read. The state machine transitions to Queue_D2 when Rd_Data_Valid is ‘1’.

Otherwise, the state machine remains in this state.

Queue_D2

State that indicates the second word has been saved to the FIFO during a burst

read. The state machine transitions to Queue_D1 if the reading of the data is

not complete when Rd_Valid is ‘1’. When done reading data from the DDR-2

controller, the state machine transitions to the FIFO_Read state.

FIFO_Read

This state is used to wait for the FIFO state machine to complete the transfer of

data read from the DDR-2 memory controller to the PLB slave. The state

machine transitions to the Idle state when the burst transfer to the PLB slave is

completing the last word in the transfer.