Opus card – ddr-2 interface – Digilent DDR-2 Opus Card User Manual

Page 13

Opus Card – DDR-2 Interface

Reference Manual

12/03/2010 07:35 AM

13

Copyright © 2009-2010 by CML

3. State Machines for Reading Data from Memory

This chapter covers the state machines that controls the reading of data requested via the PLB

bus from the DDR-2 Memory Controller. The read state machines support both non-burst reads

and burst reads. Burst reads are limited to a multiple of four 32-bit words or a multiple of two

64-bit words depending on the width of the PLB data bus and should be limited to a maximum

length of eight quad-words (128 bytes). Each burst is assumed to have consecutive addresses

starting with an address masked by 0xFFFFFFF0.

There are two state machines used for reading data from memory. The first is the read state

machine and the second is the read FIFO state machine. The first state machine controls the

reading of data from the DDR-2 memory controller to the read FIFO. To parallelize the reading

and writing to the read FIFO, the FIFO state machine was implemented to transfer data in the

FIFO to the PLB slave controller.

3.1 Signal Definitions

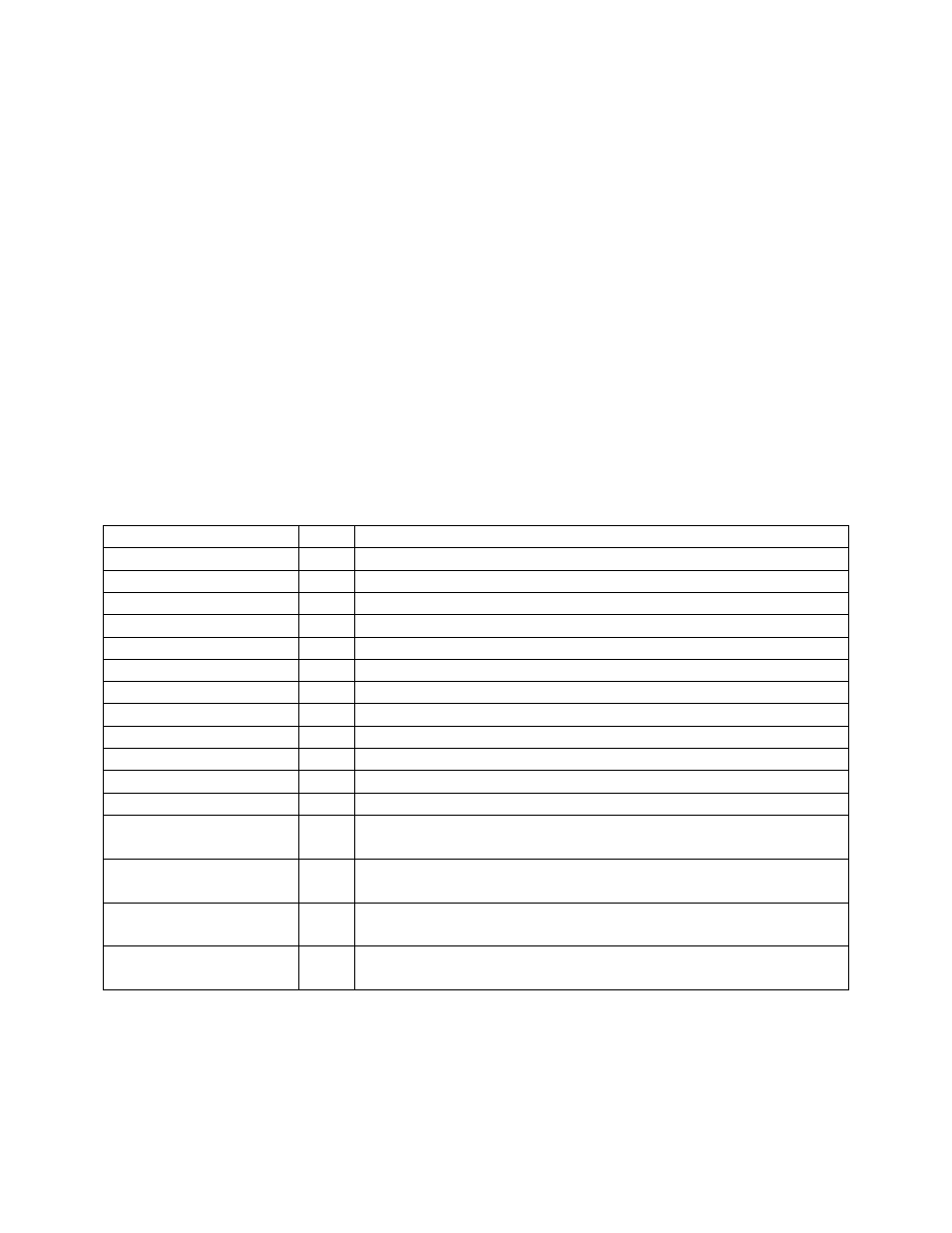

The table below provides details on the signals used for reading data from memory.

Name

I/O

Description

Bus2IP_Clk

I

The clock for the PLB bus (currently 100 MHz)

DDR2_Clk

I

The clock for the DDR-2 memory (currently 200 MHz)

Bus2IP_Reset

I

Reset signal for the block

App_AF_AFull

I

Indicates the DDR-2 address buffer is full – not currently used

Bus2IP_Addr

I

Address of DDR-2 memory to read from

Bus2IP_CS

I

Indicates the DDR-2 memory is being accessed

Bus2IP_Burst

I

Indicates a burst read or write is occurring

Bus2IP_BurstLength

I

Indicates the length of the burst in bytes

Bus2IP_RNW

I

Indicates a read access when high

Bus2IP_RdReq

I

Indicates a read request

Rd_Data_Valid

I

Indicates the data is valid from the DDR-2 memory controller

Rd_Data_FIFO_Out

I

Data read from the DDR-2 memory

IP2Bus_Data

O

Data read from the DDR-2 memory that is returned to the PLB

slave when IP2Bus_RdAck is asserted

Rd_Burst_Cnt

O

Current burst count value that is added to App_AF_AAFull

during a burst read

Rd_Send_Ack

O

Acknowledges the read from the PLB slave and signals that the

IP2Bus_Data is valid during the next clock cycle

Rd_Send_Cmd

O

Indicates the read command and address should be sent to the

DDR-2 memory controller on the next clock cycle