Ethernet phys, Loc = k1, Net pcie-rx1_n – Digilent 6015-410-001P-KIT User Manual

Page 19: Loc = l3, Net pcie-tx1_n, Loc = m2, Net pcie-rx2_p, Loc = n4, Net pcie-tx2_p, Loc = m1

NetFPGA-1G-CML™ Board Reference Manual

NET pcie-rx1_n

LOC = K1;

NET pcie-tx1_n

LOC = L3;

NET pcie-rx2_p

LOC = M2;

NET pcie-tx2_p

LOC = N4;

NET pcie-rx2_n

LOC = M1;

NET pcie-tx2_n

LOC = N3;

NET pcie-rx3_p

LOC = M2;

NET pcie-tx3_p

LOC = N4;

NET pcie-rx3_n

LOC = M1;

NET pcie-tx3_n

LOC = N3;

NET pcie-clk_p

LOC = H6;

NET pcie-clk_n

LOC = H5;

NET pcie-perstn

LOC = L17

IOSTANDARD = LVCMOS33

PULLUP

NODELAY;

NET pcie-wake

LOC = K18

IOSTANDARD = LVCMOS33;

NET pcie-prsnt

LOC = AA7

IOSTANDARD = LVCMOS18;

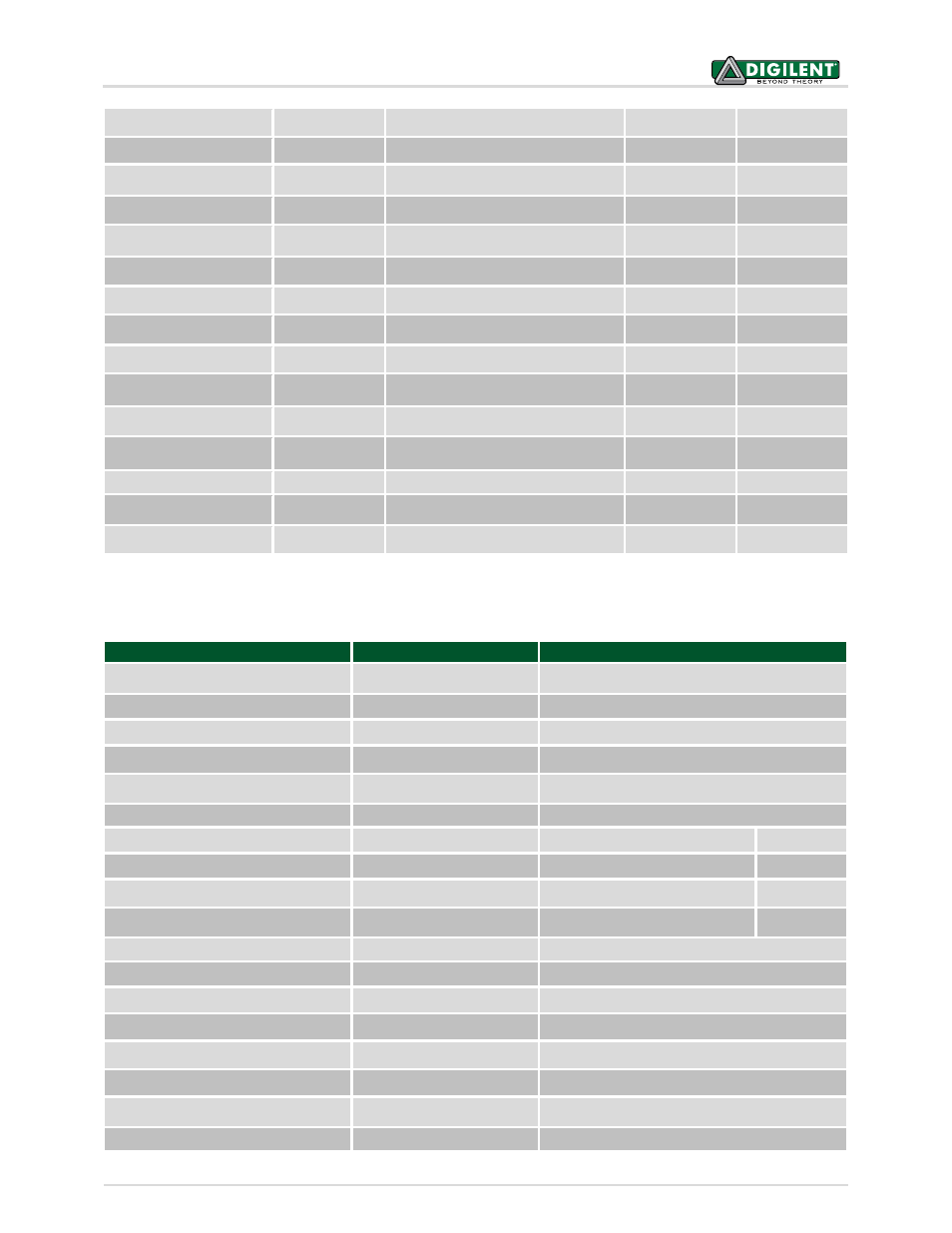

Ethernet PHYS

Port Name

IO Location

IO Standard Type

NET mdc LOC = V13

IOSTANDARD = LVCMOS18;

NET mdio LOC = W13

IOSTANDARD = LVCMOS18;

NET phy_rstn_1 LOC = K21

IOSTANDARD = LVCMOS33;

NET phy_rstn_2 LOC = L23

IOSTANDARD = LVCMOS33;

NET phy_rstn_3 LOC = E25

IOSTANDARD = LVCMOS33;

NET phy_rstn_4 LOC = D18

IOSTANDARD = LVCMOS33;

NET phy_intrn_1

LOC = J8

IOSTANDARD = LVCMOS18 PULLUP;

NET phy_intrn_2

LOC = J14

IOSTANDARD = LVCMOS18 PULLUP;

NET phy_intrn_3

LOC = K15

IOSTANDARD = LVCMOS18

PULLUP;

NET phy_intrn_4

LOC = M16

IOSTANDARD = LVCMOS18 PULLUP;

NET rgmii_rxd_1[0] LOC = A14

IOSTANDARD = LVCMOS18;

NET rgmii_rxd_1[1] LOC = B14

IOSTANDARD = LVCMOS18;

NET rgmii_rxd_1[2] LOC = E12

IOSTANDARD = LVCMOS18;

NET rgmii_rxd_1[3] LOC = D13

IOSTANDARD = LVCMOS18;

NET rgmii_txd_1[0] LOC = G12

IOSTANDARD = LVCMOS18;

NET rgmii_txd_1[1] LOC = F13

IOSTANDARD = LVCMOS18;

NET rgmii_txd_1[2] LOC = F12

IOSTANDARD = LVCMOS18;

NET rgmii_txd_1[3] LOC = H11

IOSTANDARD = LVCMOS18;

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Page 19 of 26