14 fmc expansion connector, Fmc expansion connector – Digilent 6015-410-001P-KIT User Manual

Page 11

NetFPGA-1G-CML™ Board Reference Manual

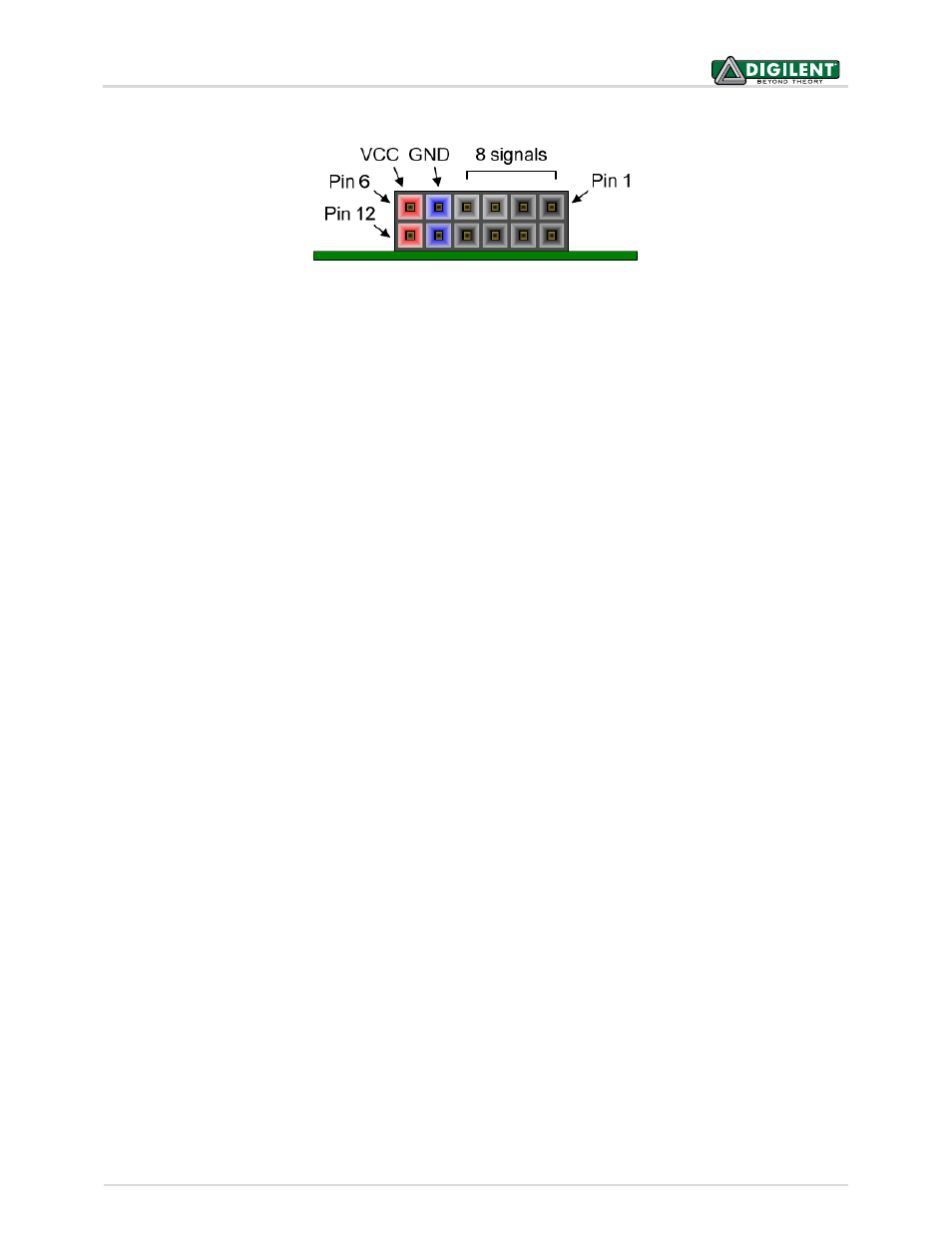

Figure 2. Pmod Connectors, End View.

14 FMC Expansion Connector

The NetFPGA-1G includes a VITA-57 compatible FMC (FPGA Mezzanine Card) carrier connector. A High Pin Count

(HPC) connector is used to provide the maximum possible compatibility with a variety of commercially available

mezzanine cards. Select I/O ports on the XC7K325T are connected to all of the standard Low Pin Count (LPC)

signals on the connector, but only 22 of the HPC signals are supported due to the limitations of the FF676 package.

Up to four differential send/receive pairs for GTX transceivers are also supported.

The FMC interface signals are driven by two Select I/O banks within the FPGA. Signal drive voltages within these

banks are configured together to match the various requirements of different mezzanine cards. These banks are

disabled on the board when shipped, but jumper JP5 (VADJ ENABLE) can be installed to prepare these I/O banks

for use with the FMC connector. Three control outputs are then included in the FPGA design configuration to set

the FMC signaling voltage and enable it. Those signals are VADJ_EN, SET_VADJ1, SET VADJ2, and are set according

to Table 1. Keep in mind that the IOSTANDARD required by the pin constraints associated with the FMC interface

will depend upon the VADJ selected, and that these VADJ programming signals should be set to constants within

the design.

Please refer to the American National Standards Institute ANSI/VITA 57.1 FPGA Mezzanine Card (FMC) Standard for

additional detail regarding standard FMC module and carrier requirements. Refer to Appendix B for specific I/O

constraints relating FPGA pins to their associated FMC control and connector pins.

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Page 11 of 26