Digilent 6015-410-001P-KIT User Manual

Page 14

NetFPGA-1G-CML™ Board Reference Manual

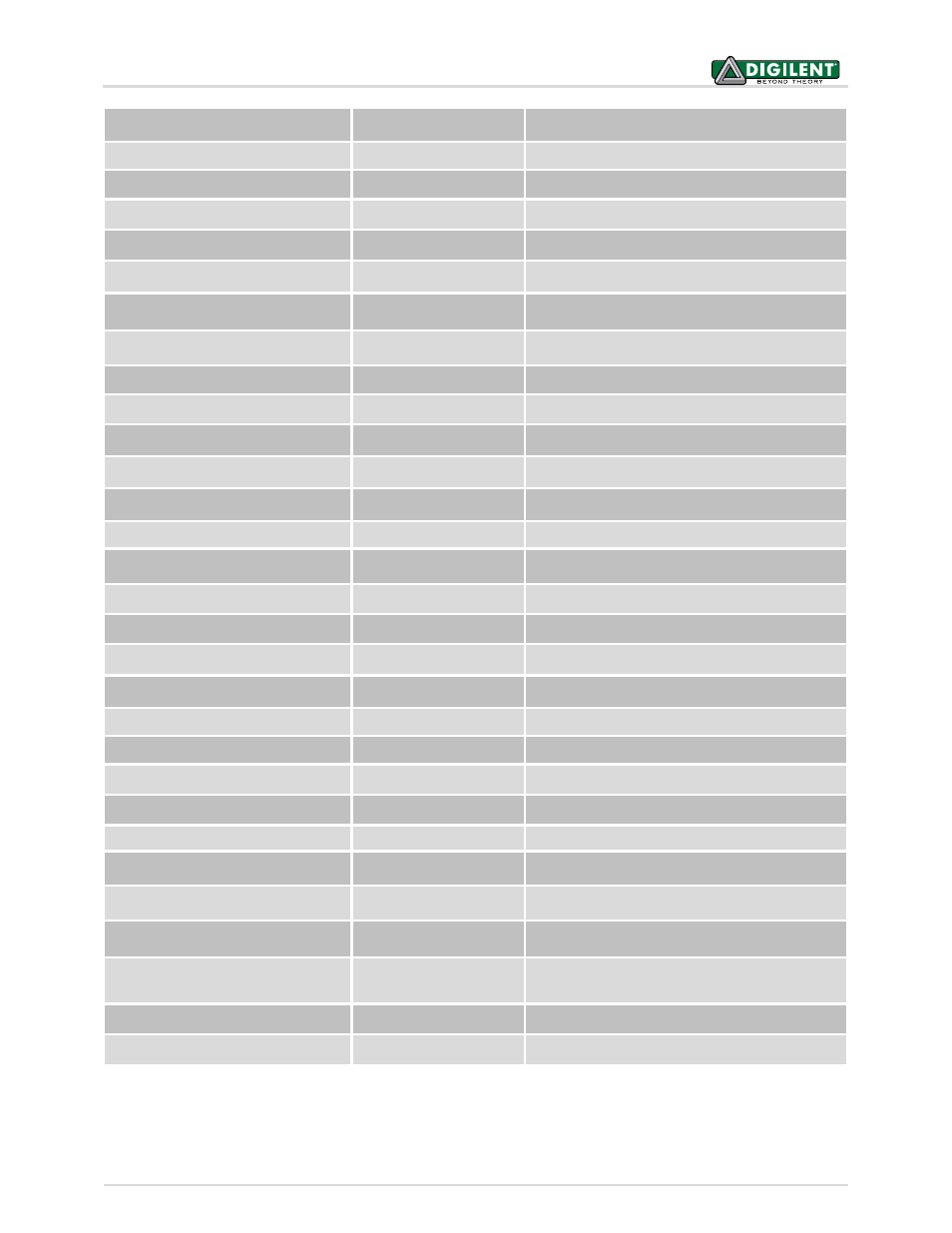

NET ddr3_addr[1]

LOC = Y2

IOSTANDARD = SSTL15;

NET ddr3_addr[2]

LOC = W3

IOSTANDARD = SSTL15;

NET ddr3_addr[3]

LOC = W5

IOSTANDARD = SSTL15;

NET ddr3_addr[4]

LOC = AB2

IOSTANDARD = SSTL15;

NET ddr3_addr[5]

LOC = W1

IOSTANDARD = SSTL15;

NET ddr3_addr[6]

LOC = AC2

IOSTANDARD = SSTL15;

NET ddr3_addr[7]

LOC = U2

IOSTANDARD = SSTL15;

NET ddr3_addr[8]

LOC = AB1

IOSTANDARD = SSTL15;

NET ddr3_addr[9]

LOC = V1

IOSTANDARD = SSTL15;

NET ddr3_addr[10]

LOC = AD6

IOSTANDARD = SSTL15;

NET ddr3_addr[11]

LOC = Y1

IOSTANDARD = SSTL15;

NET ddr3_addr[12]

LOC = AC3

IOSTANDARD = SSTL15;

NET ddr3_addr[13]

LOC = V2

IOSTANDARD = SSTL15;

NET ddr3_addr[14]

LOC = AC1

IOSTANDARD = SSTL15;

NET ddr3_addr[15]

LOC = AD5

IOSTANDARD = SSTL15;

NET ddr3_ba[0]

LOC = AA5

IOSTANDARD = SSTL15;

NET ddr3_ba[1]

LOC = AC4

IOSTANDARD = SSTL15;

NET ddr3_ba[2]

LOC = V4

IOSTANDARD = SSTL15;

NET ddr3_ras_n

LOC = Y6

IOSTANDARD = SSTL15;

NET ddr3_cas_n

LOC = Y5

IOSTANDARD = SSTL15;

NET ddr3_we_n

LOC = U5

IOSTANDARD = SSTL15;

NET ddr3_reset_n

LOC = U1

IOSTANDARD = LVCMOS15;

NET ddr3_cke[0]

LOC = AB5

IOSTANDARD = SSTL15;

NET ddr3_odt[0]

LOC = U7

IOSTANDARD = SSTL15;

NET ddr3_cs_n[0]

LOC = U6

IOSTANDARD = SSTL15;

NET ddr3_dm[0]

LOC = AE6

IOSTANDARD = SSTL15;

NET ddr3_dqs_p[0]

LOC = AF5

IOSTANDARD = DIFF_SSTL15_T_DCI;

NET ddr3_dqs_n[0]

LOC = AF4

IOSTANDARD = DIFF_SSTL15_T_DCI;

NET ddr3_ck_p[0]

LOC = AA4

IOSTANDARD = DIFF_SSTL15;

NET ddr3_ck_n[0]

LOC = AB4

IOSTANDARD = DIFF_SSTL15;

Copyright Digilent, Inc. All rights reserved.

Other product and company names mentioned may be trademarks of their respective owners.

Page 14 of 26