Kx-p1150 – Panasonic KX-P1150 User Manual

Page 27

Attention! The text in this document has been recognized automatically. To view the original document, you can use the "Original mode".

KX-P1150

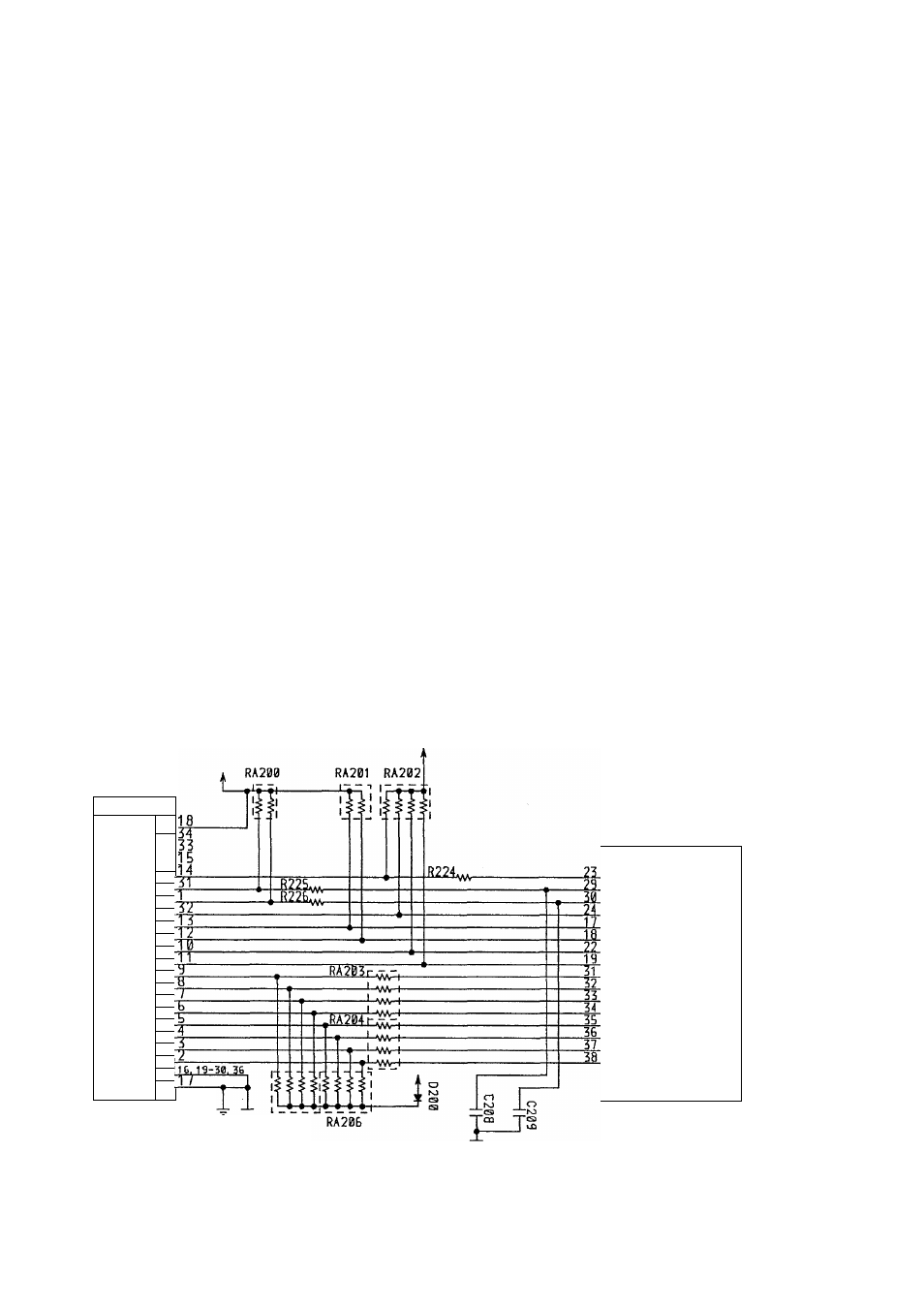

8.2.3 Parallel Interface Circuit

The Interface Block receives data from the host computer and generates the appropriate status signals.

The handshake method is described in the following steps.

Process

(1) A STROBE signal is sent from the host computer and is used to set the internal latch of the Gate Array. At

the same time Gate Array pin (

3

) sends a BUSY signal to the host computer.

_______

(2) The CPU checks the internal latch of the Gate Array periodically and checks whether a STROBE is sent or

not_______

(3) If a STROBE signal has been sent, the CPU reads the data through HS ports (HS0-HS7) of the Gate Array.

(4) When the BUSY signal disappears, an ACK (Acknowledge) signal is sent to the host computer

automatically during the time determined by software.

(5) The CPU then determines from the received data as to wheter it is a character code, control code or bit

image data and processes the data accordingly.

(

6

) The CPU processes another command (for instance: operation swtich state check, motor drive during

print).

Thus the data received by handshake is accomplished.

Timing Chart

Data 1-8 from HOST —

STROBE from HOST

BUSY to HOST (pin (

1

^ )

ACK to HOST (pin ^ )

r

«

Printer

HOST

Handshake

j

CN205

-T5V

0

-

EXPRM

O-

R1NF0

O-

R1NF2

O

AFXT/1 a

PRIME

0

-

STROBE O-

ERROR

a

SELECT

0

-

P.E.

O-

ACK

O-

BUSY

0

OATAB

a

DATA?

O-

DATAS

O

DATAS

a

DATA4

a

DATAS

0

DATA2

0

-

DATAI

0

GND

0

FG

0

-

IC20S

AFXT

PRIME

STB

ERROR

SELECT

PE

ACK

GATE

BUSY

ARRAY

Hb /

HS6

HS5

HS4

HS3

HS2

HS1

HS0

RA205